# *Speed* 低雑音プリアンプ付き デュアル可変ゲイン・アンプ

# 特長

#### ● 低雑音プリアンプ:

• 低入力雑音: 1.25nV/√Hz

• アクティブ終端による雑音を低減

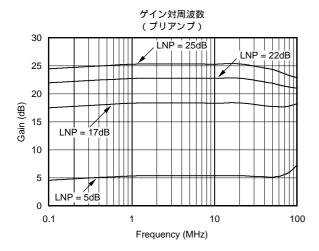

終端値を切り換え可能帯域幅:80MHzゲイン:5dB~25dB

• 差動入力/出力

#### ● 低雑音可変ゲイン・アンプ

低雑音VCA:3.3nV/√Hz、差動プログラミングにより 雑音値を最適化

ゲイン: 24dB~45dB帯域幅: 40MHz差動入力/出力

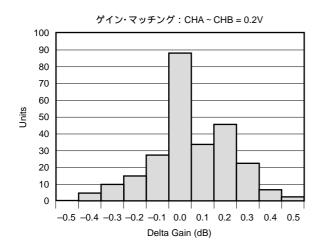

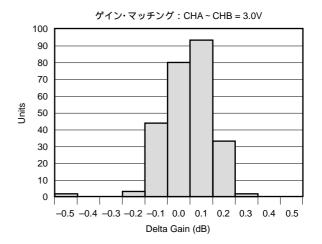

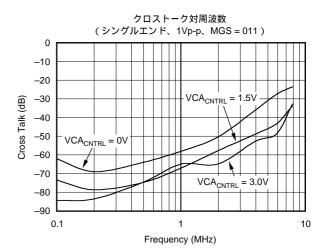

● **低クロストーク**:52dB(ゲイン最大、5MHz時)

● 高速可変ゲイン調整

● 外部処理を切り換え可能

# アプリケーション

● 超音波システム

● ワイヤレス・レシーバ

● テスト装置

### 概要

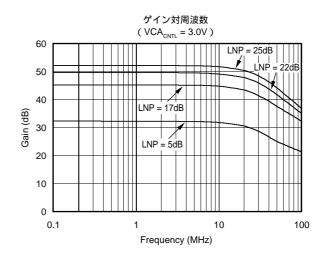

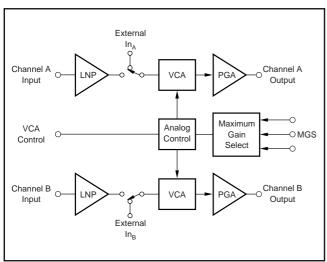

VCA2612は、高度に統合化されたデュアル受信チャンネルの信号処理サプシステムです。各チャンネルは低雑音プリアンプ(LNP)と可変ゲイン・アンプ(VGA)で構成されています。LNP回路には、アクティブ終端(AT)を実施するために必要な接続が用意されています。これは、ノイズフィギュアを最大4.6dB改善できるケーブル終端法です。LNPの切り替え可能なフィードバック・ピンを使用すれば、各種のケーブル終端特性に対応できます。LNPは、差動入力またはシングルエンド入力により、差動出力信号を生成します。LNPのゲインは5dB、17dB、22dB、25dBにストラップできます。

LNPの出力は、外部にアクセスしてさらに信号処理を行うか、または直接VGAに供給できます。VCA2612のVGA部は、電圧制御減衰器(VCA)とプログラマブル・ゲイン・アンプ(PGA)の2つの部分からなっています。プログラマブル・ゲイン・アンプのゲインおよびゲイン範囲は、デジタル・プログラミングが可能です。この2つのプログラマブルな要素の組み合わせにより、0dBからユーザが外部接続で定義する最大ゲインまでの範囲で、ゲインを調整できます。VGAの出力は、シングルエンドまたは差動モードで使用して高性能A/Dコンバータをドライブできます。

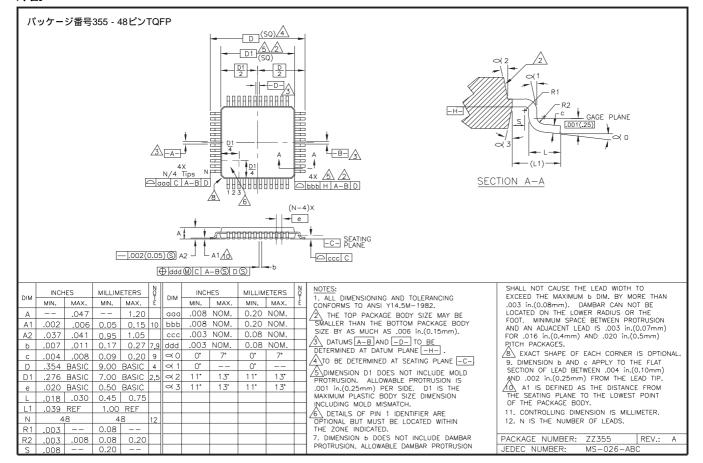

VCA2612はクロストークが低く、歪性能も優れています。低雑音、ゲイン範囲がプログラミング可能、という2つの特長により、VCA2612は、雑音性能が重要となる多くのアプリケーションで多機能ビルディング・プロックとして利用できます。パッケージは48ピンTQFPで供給されます。

PDSJ-1541B March,2000

# 仕樣

|                                                        |                                                      | VCA2612Y |          |                   |         |  |

|--------------------------------------------------------|------------------------------------------------------|----------|----------|-------------------|---------|--|

| パラメータ                                                  | 条件                                                   | 最小       | 最小 標準 最大 |                   | 単位      |  |

| プリアンプ                                                  |                                                      |          |          |                   |         |  |

| 入力抵抗                                                   |                                                      |          | 600      |                   | kΩ      |  |

| 入力容量                                                   |                                                      |          | 15       |                   | pF      |  |

| 入力バイアス電流                                               |                                                      |          | 1        |                   | nA      |  |

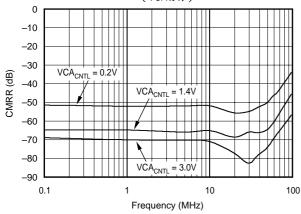

| CMRR                                                   | $f = 1MHz$ , $VCA_{CNTL} = 0.2V$                     |          | 50       |                   | dB      |  |

| 最大入力電圧                                                 | プリアンプ・ゲイン = +5dB                                     |          | 1        |                   | Vp-p    |  |

|                                                        | プリアンプ・ゲイン = +25dB                                    |          | 112      |                   | mVp-p   |  |

| 入力電圧雑音(1)                                              | プリアンプ・ゲイン = +5dB                                     |          | 3.5      |                   | nV/√ Hz |  |

|                                                        | プリアンプ・ゲイン = +25dB                                    |          | 1.25     |                   | nV/√ Hz |  |

| 入力電流雑音                                                 | Independent of Gain                                  |          | 350      |                   | fA/√Hz  |  |

| ノイズフィギュア、 $R_s = 75\Omega$ 、 $R_{IN} = 75\Omega^{(1)}$ | $R_r = 550\Omega$ 、 プリアンプ・ゲイン = +22dB、               |          | 6.2      |                   | dB      |  |

| S IN                                                   | PGAゲイン = 39dB                                        |          |          |                   |         |  |

| 帯域幅                                                    | ゲイン = 22dB                                           |          | 80       |                   | MHz     |  |

| プログラマブル可変ゲイン・アンプ                                       |                                                      |          |          |                   |         |  |

| ピーク入力電圧                                                | 差動                                                   |          | 2        |                   | Vp-p    |  |

| -3dB帯域幅                                                |                                                      |          | 40       |                   | MHz     |  |

| スルーレート                                                 |                                                      |          | 300      |                   | V/μs    |  |

| 出力信号レンジ                                                | R <sub>,</sub> ≥ 500Ω(各側、対グランド)                      |          | 2.5 ±1   |                   | ν̈́     |  |

| 出力インピーダンス                                              | f = 5MHz                                             |          | 1        |                   | Ω       |  |

| 出力短絡電流                                                 |                                                      |          | ±40      |                   | mA      |  |

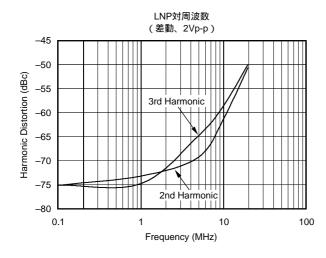

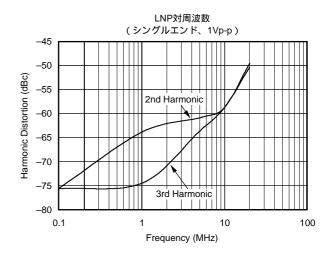

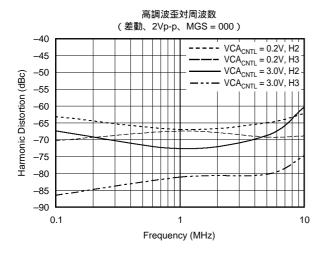

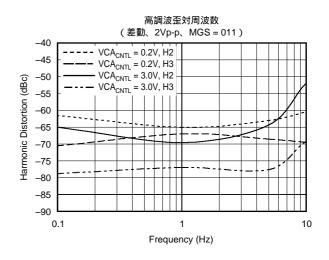

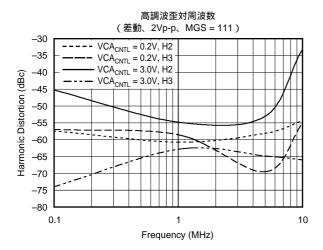

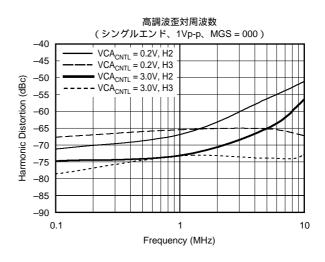

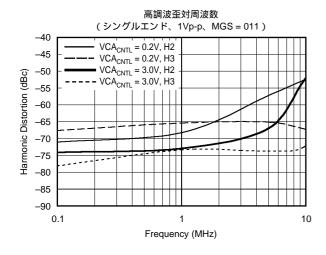

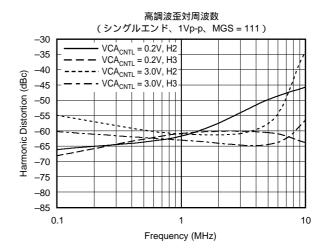

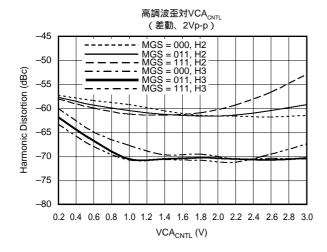

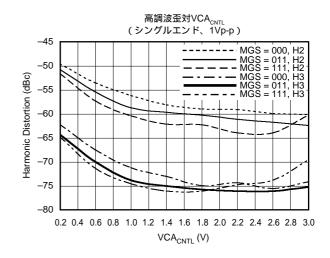

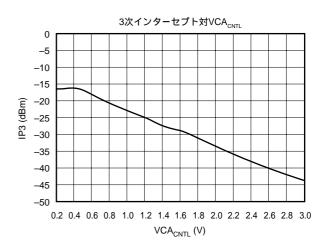

| 3次高調波歪                                                 | $f = 5MHz$ , $V_{OUT} = 1Vp-p$ , $VCA_{CNTL} = 3.0V$ | -45      | -71      |                   | dBc     |  |

| 2次高調波歪                                                 | $f = 5MHz$ , $V_{OUT} = 1Vp-p$ , $VCA_{CNTL} = 3.0V$ | -45      | -63      |                   | dBc     |  |

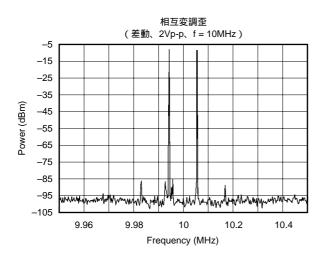

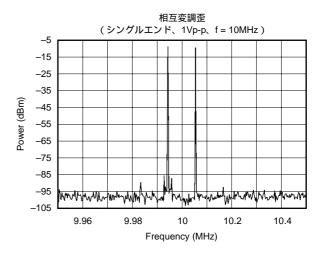

| IMD、ツー・トーン                                             | $V_{\text{OUT}} = 2Vp-p, f = 1MHz$                   |          | -80      |                   | dBc     |  |

|                                                        | $V_{OUT} = 2Vp-p, f = 10MHz$                         |          | -80      |                   | dBc     |  |

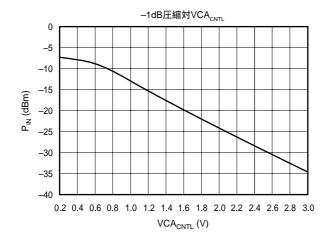

| 1dB圧縮点                                                 | f = 5MHz、出力換算、差動                                     |          | 6        |                   | Vp-p    |  |

| クロストーク                                                 | V <sub>OUT</sub> = 1Vp-p、f = 1MHz、両チャンネル最大ゲイン        |          | 68       |                   | dB      |  |

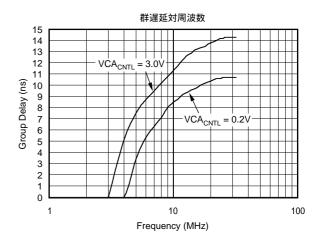

| 群遅延変動                                                  | 1MHz < f < 10MHz、ゲインの全範囲                             |          | ±2       |                   | ns      |  |

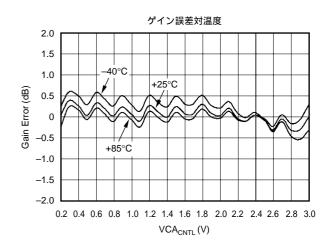

| 精度                                                     |                                                      |          |          |                   |         |  |

| ゲイン・スロープ                                               |                                                      |          | 10.9     |                   | dB/V    |  |

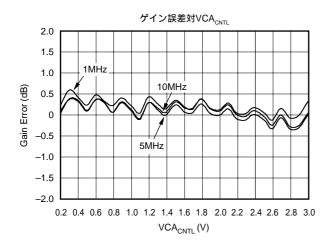

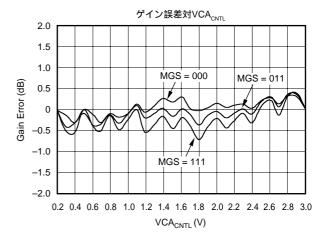

| ゲイン誤差                                                  |                                                      |          |          | ±1 <sup>(2)</sup> | dB      |  |

| 出力オフセット電圧                                              |                                                      |          | ±50      |                   | mV      |  |

| ゲイン制御インターフェース                                          |                                                      |          |          |                   |         |  |

| 入力電圧(VCA <sub>CNTI</sub> )レンジ                          |                                                      |          | 0 ~ 3.0  |                   | V       |  |

| 入力抵抗                                                   |                                                      |          | 1        |                   | MΩ      |  |

| 応答時間                                                   | 45dBのゲイン変化、MGS = 111                                 |          | 0.2      |                   | μs      |  |

| 電源                                                     |                                                      |          |          |                   |         |  |

| 仕樣動作範囲                                                 |                                                      | 4.75     | 5.0      | 5.25              | V       |  |

| 消費電力                                                   | 動作、両チャンネル                                            |          | 410      | 475               | mW      |  |

注:(1)プリアンプでVGAをドライブする場合です。(2)最も近いdBリニア曲線に換算しています。

# 静電気放電対策

この集積回路は静電気によって損傷を受ける場合があります。 すべての集積回路の取り扱いには十分な注意を払ってください。 適切な取り扱いや正しい設置手順の実行を怠った場合、損傷を与 えるおそれがあります。

静電気放電はわずかな性能の低下から完全なデバイスの故障に 至るまで、様々な損傷を与えます。高精度の集積回路は、損傷に 対して敏感であり、極めてわずかなパラメータの変化により、デ バイスに規定された仕様に適合しなくなる場合があります。

### 絶対最大定格

| 電源( +V <sub>s</sub> )<br>アナログ入力 | +6V      |

|---------------------------------|----------|

| アナログ入力                          |          |

| ロジック入力                          |          |

| ケース温度                           | +100     |

| 接合部温度                           | +150     |

| 保存温度                            | 40 ~+150 |

### パッケージ情報/ご発注の手引き

| モデル      | パッケージ    | パッケージ図番号 | 仕様温度範囲   | パッケージ・<br>マーキング | <b>発注番号</b> (1) | 供給時の状態 |

|----------|----------|----------|----------|-----------------|-----------------|--------|

| VCA2612Y | 48ピンTQFP | 355      | -40 ~+85 | A12             | VCA2612Y/250    | テープリール |

| VCA2612Y | 48ピンTQFP | 355      | -40 ~+85 | A12             | VCA2612Y/2K     | テープリール |

注:(1)スラッシュ(/)の付いたモデルは、表示数量のテープリールでのみ供給されます(たとえば、/2Kはリール1本あたり2,000個入りであることを示します)。「VCA2612Y/2K」を発注すると、2,000個入りテープリールが1本納品されます。

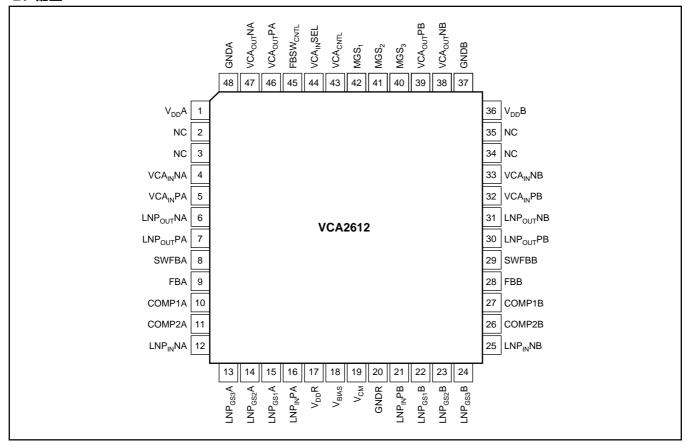

### ピン配置

### ピン構成

| ピン | 名称                    | 説明                   | ピン | 名称                    | 説明                  |

|----|-----------------------|----------------------|----|-----------------------|---------------------|

| 1  | V <sub>DD</sub> A     | チャンネルA 正電源           | 25 | LNP <sub>IN</sub> NB  | チャンネルB LNP反転入力      |

| 2  | NC                    | 接続しない                | 26 | COMP2B                | チャンネルB 周波数補償2       |

| 3  | NC                    | 接続しない                | 27 | COMP1B                | チャンネルB 周波数補償1       |

| 4  | VCA <sub>IN</sub> NA  | チャンネルA VCA負入力        | 28 | FBB                   | チャンネルB 帰還出力         |

| 5  | VCA <sub>IN</sub> PA  | チャンネルA VCA正入力        | 29 | SWFBB                 | チャンネルB 切り換え帰還出力     |

| 6  | LNP <sub>out</sub> NA | チャンネルA LNP負出力        | 30 | LNP <sub>out</sub> PB | チャンネルB LNP正出力       |

| 7  | LNP <sub>out</sub> PA | チャンネルA LNP正出力        | 31 | LNP <sub>OUT</sub> NB | チャンネルB LNP負出力       |

| 8  | SWFBA                 | チャンネルA 切り換え帰還出力      | 32 | VCA <sub>IN</sub> PB  | チャンネルB VCA正入力       |

| 9  | FBA                   | チャンネルA 帰還出力          | 33 | VCA <sub>IN</sub> NB  | チャンネルB VCA負入力       |

| 10 | COMP1A                | チャンネルA 周波数補償1        | 34 | NC                    | 接続しない               |

| 11 | COMP2A                | チャンネルA 周波数補償2        | 35 | NC                    | 接続しない               |

| 12 | LNP <sub>IN</sub> NA  | チャンネルA LNP反転入力       | 36 | V <sub>DD</sub> B     | チャンネルB 正アナログ電源      |

| 13 | LNP <sub>GS3</sub> A  | チャンネルA LNPゲイン・ストラップ3 | 37 | GNDB                  | チャンネルB アナログ・グランド    |

| 14 | LNP <sub>GS2</sub> A  | チャンネルA LNPゲイン・ストラップ2 | 38 | VCA <sub>OUT</sub> NB | チャンネルB VCA負出力       |

| 15 | LNP <sub>GS1</sub> A  | チャンネルA LNPゲイン・ストラップ1 | 39 | VCA <sub>OUT</sub> PB | チャンネルB VCA正出力       |

| 16 | LNP <sub>IN</sub> PA  | チャンネルA LNP非反転入力      | 40 | MGS₃                  | 最大ゲイン選択3( LSB )     |

| 17 | V <sub>DD</sub> R     | 内部リファレンス用正電源         | 41 | MGS <sub>2</sub>      | 最大ゲイン選択2            |

| 18 | V <sub>BIAS</sub>     | 0.01μFバイパス( 対グランド )  | 42 | MGS₁                  | 最大ゲイン選択1( MSB )     |

| 19 | V <sub>CM</sub>       | 0.01μFバイパス( 対グランド )  | 43 | VCA <sub>CNTL</sub>   | VCA制御電圧             |

| 20 | GNDR                  | 内部リファレンス用グランド        | 44 | VCA <sub>IN</sub> SEL | VCA入力選択、" ハイ "= 外部  |

| 21 | LNP <sub>IN</sub> PB  | チャンネルB LNP非反転入力      | 45 | FBSW <sub>CNTL</sub>  | 帰還切り換え制御:" ハイ "= オン |

| 22 | LNP <sub>GS1</sub> B  | チャンネルB LNPゲイン・ストラップ1 | 46 | VCA <sub>OUT</sub> PA | チャンネルA VCA正出力       |

| 23 | LNP <sub>GS2</sub> B  | チャンネルB LNPゲイン・ストラップ2 | 47 | VCA <sub>OUT</sub> NA | チャンネルA VCA負出力       |

| 24 | LNP <sub>GS3</sub> B  | チャンネルB LNPゲイン・ストラップ3 | 48 | GNDA                  | チャンネルA アナログ・グランド    |

特に記述のない限り、 $T_{_{\Lambda}}$  = +25 、 $V_{_{DD}}$  = 5V、各出力の対グランド負荷抵抗 = 500 $\Omega$ 、MGS = 011、LNP = 22dB、 $f_{_{IN}}$  = 5MHz。プリアンプ( LNP )への入力はシングルエンド、VCAからの出力はシングルエンドです。

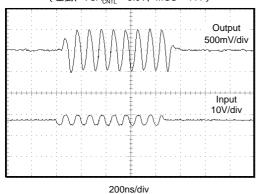

パルス応答(バースト) (差動、 $VCA_{CNTL} = 3.0V$ 、MGS = 111)

200ns/div

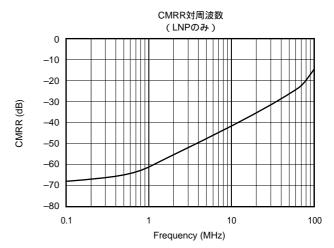

#### CMRR対周波数 (VCAのみ)

# 動作原理

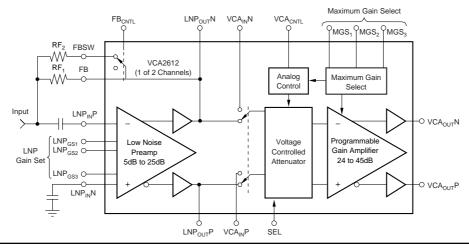

VCA2612は、3つの主要ブロック、低雑音アンプ(LNP)、電圧制御減衰器(VCA)、プログラマブル・ゲイン・アンプ(PGA)から構成されるデュアル・チャンネル・システムです。システムの柔軟性を高めるために、VCAの入力にはオンボード・マルチプレクサが備えられ、LNP出力または外部信号入力のいずれかを選択できます。図1に、このデュアル・チャンネル・システムの概略ブロック図を示します。

図1. VCA2612の概略プロック図

#### LNP 概要

LNPの入力は、アクティブ・フィードバック信号終端を行う接 続が可能です。これにより、従来のパッシブなシャント終端より も低いシステム雑音性能を実現できます。信号の終端が必要なけ れば、さらに雑音を低減することができます。非終端LNP入力イ ンピーダンスは600kΩです。LNPは各チャンネルにおいて、完全 に差動な信号またはシングルエンドの信号を処理できます。差動 信号処理を行うと、2次高調波歪が大きく低減され、同相モード および電源雑音の除去が向上します。LNPの最初のゲイン段は、 44µsの時定数(3.6kHzのハイパス特性)でその出力バッファにAC 結合されています。バッファリングされたLNP出力は、次段の VCAを直接ドライブするか、または必要であれば、最低135Ωま での外部負荷を信号歪への影響を最小限にしてドライブすること ができます。LNPはインピーダンスが非常に低いローカル・ フィードバックによって、可能な限り低い雑音と歪で安定したゲ インを得ています。ピン・プログラミングにより、4種類のゲイン (5dB、17dB、22dB、25dB)が設定できます。ゲイン・ストラッ プ・プログラミング・ピンの間に調整抵抗を追加すれば、その中間 のゲインもプログラムできます。

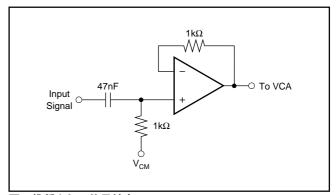

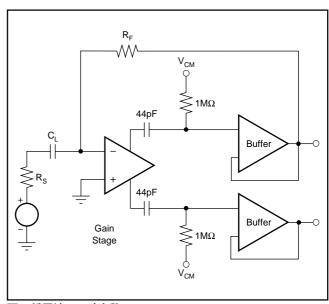

LNP出力の同相モードDCレベルは公称2.5Vで、単純な直接結合においてVCAの入力同相モード条件に一致しています。VCAに外部信号を供給する場合は、やはりDC2.5Vの同相モード・レベルを設定する必要があります。図2の回路は、外部オペアンプを使用した推奨結合方法を示すものです。図中で"V<sub>CM</sub>"と示される

ノードは、V<sub>CM</sub>出力(ピン19)です。LNPと同様のハイパス時定数を得る標準的なRとCの値が示されています。これ以外の方法で同相モード・リファレンスを接続する場合、正しい動作を得るためには、同相モード・レベルがV<sub>CM</sub>出力の10m√以内であることが重要です。

図2. 推奨される信号結合

#### VCA 概要

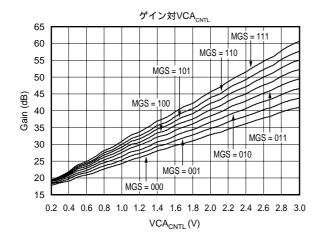

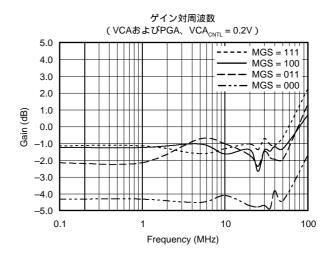

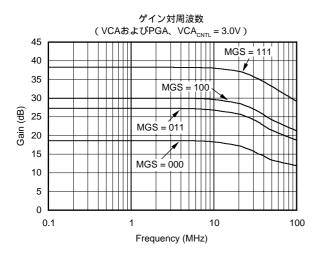

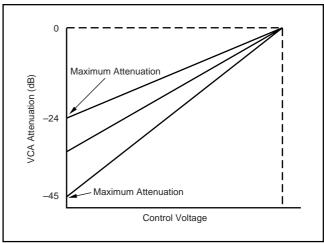

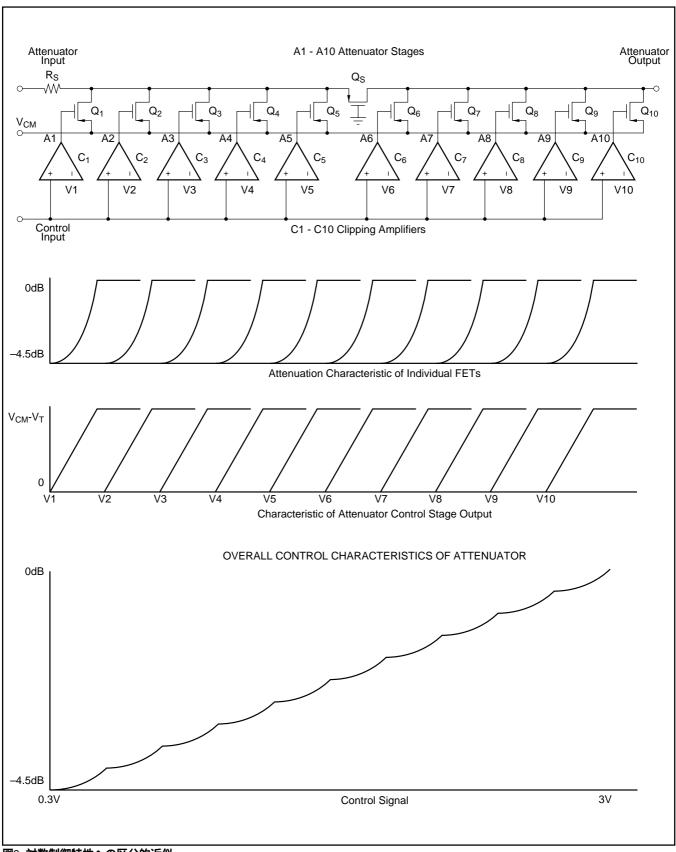

差動VCA入力信号(LNPまたは外部ソースから入力)の大きさは、プログラマブルな減衰係数によって低減されます。これは、ピン43のアナログVCA制御電圧(VCA<sub>CNTL</sub>)によって設定されます。さらに、3つのMGSピット(ピン40~42)を使用して、減衰係数の最大値をプログラムできます。この2段階調整が可能な特性を図3に示します。内部では、アナログVCA<sub>CNTL</sub>によって一連のシャント接続FETトランジスタのチャンネル抵抗を変化させることで、信号を減衰させています。MGSピットは、ロジック制御の並列成分の接続を切り換えることで、シャントFETの全体サイズを効果的に調整します。ゲイン設定の最大値が与えられると、アナログ可変ゲイン特性は制御電圧の関数としてdBについてリニアになり、理想的なdBリニア伝達関数の区分的近似となります。VCAゲイン制御回路は、VCA2612の両方のチャンネルに共通です。

図3. 掃引減衰器特性

### PGAの概要とデバイス全体の特性

VCA減衰器の差動出力はPGA回路ブロックによって増幅されます。このポストアンプは、VCA減衰器の制御用と同じMGSビットによってプログラムされ、全体の掃引ゲイン・アンプ特性が得られます。VCA・PGAゲインは、0dB(ユニティ)からプログラマブルなピーク・ゲイン(24、27、30、33、36、39、42、45dB)までの範囲で可変です。

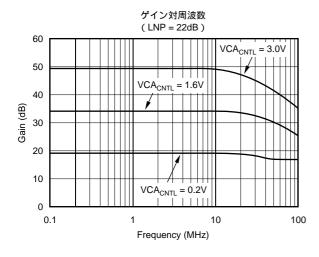

5ページの「ゲイン対VCA<sub>CNTL</sub>」曲線には、VCA2612全体の複合ゲイン制御特性が示されています。VCA<sub>CNTL</sub>を3.0Vに設定すると、デジタルMGSゲイン制御は3dB間隔になります。VCA<sub>CNTL</sub>を0Vに設定すると、すべてのMGS制御ゲイン曲線が1点に収束します。収束点でのゲインはLNPゲイン-6dBです。これは、測定用設定では差動PGA出力の一方しか観測されず、6dB低い信号振幅となるからです。

#### その他の機能 概要

減衰器とPGAの間には過負荷保護段が配置され、PGAが過負荷になる位に入力が大きくなると、出力を対称的にクリッピングします。コンパレータが過負荷信号振幅を検知して、それを固定DCレベルに置き換えることで、過負荷復帰による望ましくない影響を防ぎます。前の各段と同様に、VCAはPGAにAC結合されます。この場合、結合時定数はゲイン最大(46dB)時の5μsからゲイン最小(25dB)時の59μsまで変化します。

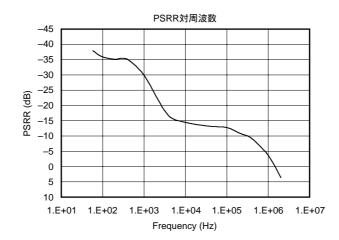

VCA2612には、両チャンネルに共通の内蔵リファレンスが含まれ、回路内の重要な領域に対して安定した電圧を供給します。こ

れにより、電源の変動、リップルおよび雑音による影響が低減されます。また、各チャンネルおよびリファレンス回路には個別の電源とグランド接続があり、チャンネル間クロストークがさらに低減されます。

各回路プロックの設計、動作、使用法の詳細について、以降の 節で説明します。

#### 低雑音プリアンプ(LNP) 詳細

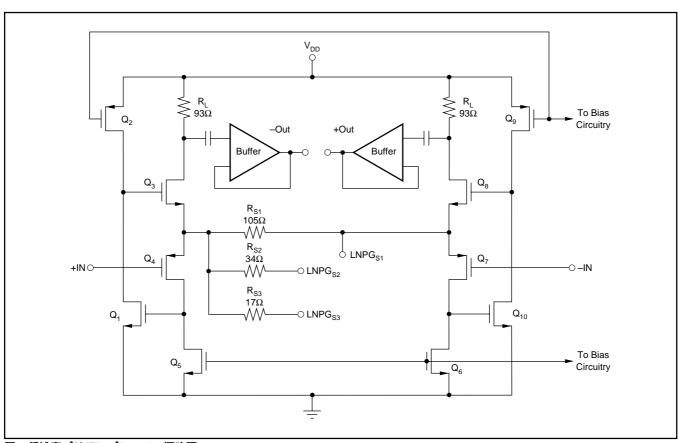

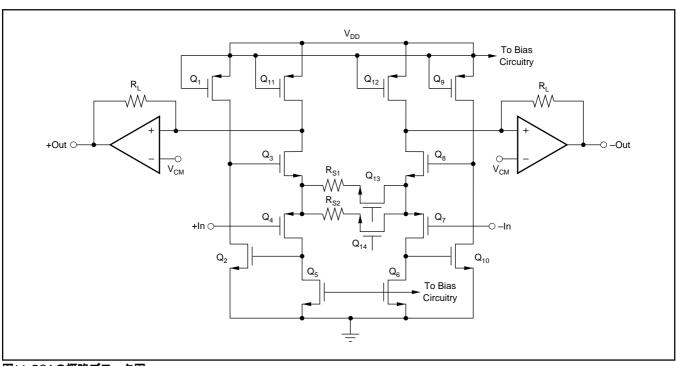

LNPは、アクティブ終端を使用したときに特に低い雑音値が得られるように設計されています。図4はLNPの概略図であり、差動入力/出力の機能を示しています。入力段は低抵抗ローカル・フィードバックにより、安定した低雑音、低歪性能を非常に高い入力インピーダンスで実現しています。通常、低雑音回路では、入力段と出力段の両方で大きなバイアス電流が必要になるため、消費電力が大きくなります。LNPでは、特許取得済みの技法を用いて、同じバイアス電流を共用するように入力段と出力段を結合しています。トランジスタQ4およびQ5はQ4のゲート・ソース入力(LNPの+IN側)で信号を増幅します。信号はQ1およびQ2段によってさらに増幅されてから、最終のQ3およびR\_ゲイン段によって増幅されます。最終段では入力デバイスQ4およびQ5と同じバイアス電流を使用します。-IN側の信号に対しては、デバイスQ6~Q10が同様に機能します。LNPの差動ゲインは式(1)で求められます。

Gain =

$$2 \cdot \left[ \frac{R_L}{R_s} \right]$$

(1)

図4. 低雑音プリアンプ(LNP)の概略図

ここで $R_L$ はQ3およびQ8のドレインの負荷抵抗であり、 $R_s$ は入カトランジスタQ4およびQ7のソース間に接続される抵抗です。デバイスのピンLNPG $_{S1}$ 、LNPG $_{S2}$ 、LNPG $_{S3}$ 、チャンネルAはピン13~15、チャンネルBはピン22~24)の接続によって、各種の $R_s$ を組み合わせることができます。これらのゲイン・ストラップ・ピンを使用して、ユーザーは表に示す4つの固定LNPゲイン・オプションのいずれかを設定できます。

| LNPピンのストラップ                                                       | LNP <b>ゲイン(</b> dB) |

|-------------------------------------------------------------------|---------------------|

| LNPG <sub>s1</sub> 、LNPG <sub>s2</sub> 、LNPG <sub>s3</sub> をすべて接続 | 25                  |

| LNPG <sub>s1</sub> をLNPG <sub>s3</sub> に接続                        | 22                  |

| LNPG <sub>s1</sub> をLNPG <sub>s2</sub> に接続                        | 17                  |

| すべて <sup>°</sup> のピンをオープン                                         | 5                   |

表 LNPのピン・ストラップと対応するゲイン

また、一方の側(LNPG $_{S1}$ )ともう一方の側(LNPG $_{S2}$ かLNPG $_{S3}$ 、またはその両方)の間に外部抵抗を接続することにより、上記以外のゲインを設定することもできます。その場合は、図4に示す内部抵抗値を外部抵抗と組み合わせて、式(1)で使用する $R_{S}$ の有効値を計算する必要があります。その結果、外部抵抗値を求める式は式(2)で与えられます。

$$R_{EXT} = \frac{2R_{S1}R_L + 2R_{FIX}R_L - Gain \cdot R_{S1}R_{FIX}}{Gain \cdot R_{S1} - 2R_L}$$

(2)

ここで $R_{\rm EXT}$ は、必要なゲイン設定を得るために外部で選択する抵抗値です。 $R_{\rm S1}$ は図4の固定並列抵抗であり、 $R_{\rm FIX}$ はもう一方の内部抵抗(ピン接続に応じて $R_{\rm S2}$ 、 $R_{\rm S3}$ 、または $R_{\rm S2}$   $||R_{\rm S3}$  の実効固定値です。

プロセスおよび温度に対する安定性が最高になるのは、表1のプログラム済み固定ゲイン・オプションを使用した場合であることに注意してください。これは、ゲインが完全に内部抵抗比で設定されるためです。この場合、ゲインは標準で±0.5%の精度を持ち、プロセスおよび温度の変化に対して十分に追従します。外部抵抗を内部値と組み合わせて実効R<sub>S</sub>値を作成する場合には、内部抵抗の標準温度係数が+700ppm/ で絶対値公差が約±5%であり、ゲイン設定の予測可能性と安定性がやや低下することに注意してください。外部抵抗を使用するかしないかにかかわらず、基板レイアウトではゲイン・ストラップ接続をできるだけ短くして、寄生抵抗およびインダクタンスの影響を最小限に抑えるようにします。

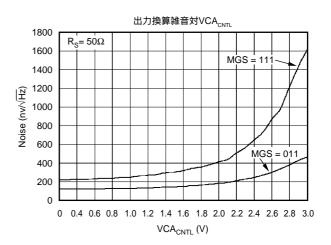

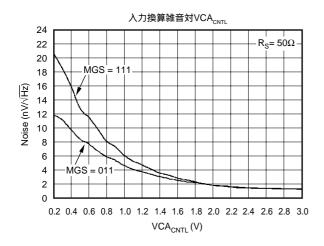

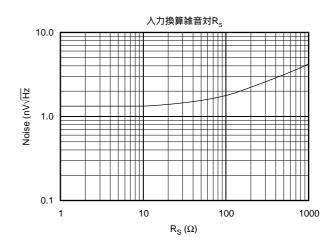

VCA2612の全体の雑音性能は、ゲインの関数として変化します。表に、最大のVCAおよびPGAゲインを得るときのVCA2612全体の入力換算および出力換算雑音密度の標準値を示します。このとき、VCA<sub>CNTL</sub>は3.0Vに設定され、MGSビットはすべで"1"に設定されています。入力換算雑音値には50Ωの固定ソース・インビーダンスの寄与が含まれ、そのために固有の入力雑音よりもやや大きな値になることに注意してください。LNPゲインが小さくなると、VCA/PGA部分からの雑音寄与が比重を増し、入力換算雑音が高くなります。ただし、そのゲイン設定での全体のSNRの指標である出力換算雑音は、低下します。

LNPの低雑音性能を保持するためには、入力ピンの抵抗をできる限り低くする必要があります。わずか $10\Omega$ の寄生抵抗でも0.4n $V/\sqrt{Hz}$ の寄与があります。

| LNP <b>ゲイン(</b> dB) | <b>雑音(</b> nV/√Hz ) |      |

|---------------------|---------------------|------|

| LINPO 1 D( GB)      | 入力換算                | 出力換算 |

| 25                  | 1.54                | 2260 |

| 22                  | 1.59                | 1650 |

| 17                  | 1.82                | 1060 |

| 5                   | 4.07                | 597  |

表 . MGS = 111およびVCA<sub>CNTL</sub> = 3.0V**での雑音性能**

LNPは、2Vp-pの差動信号を生成することができます。したがって、LNP入力における最大信号は、2Vp-pをLNPゲインで割ったものになります。これより大きな入力信号は、LNPのリニアな動作範囲を超えます。これはLNPゲイン設定が低い場合には特に重要な考慮点です。

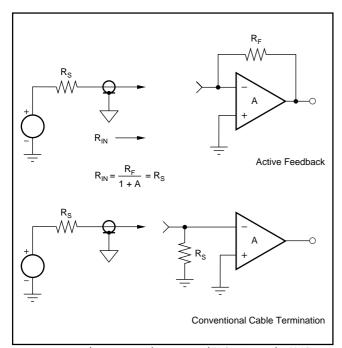

#### LNPでのアクティブ・フィードバック

LNPのアーキテクチャの主要な特長の1つが、アクティブ・ フィードバック終端の使用によって優れた雑音性能を達成できる ことです。アクティブ・フィードバック終端を使用すると、従来 のシャント終端よりも低い雑音値が得られます。これは基本的 に、終端抵抗自体で信号電流を消費しないからです。また、これ は次のように理解することもできます。まず、信号ケーブルの向 こう側にある入力ソースにおいて、ケーブル・マッチング・ソース 抵抗の値がR。であるとします。LNP入力で従来のシャント終端を 使用して、値がR。の第2の終端抵抗をグランドに接続します。こ のとき、直列およびシャントのR。抵抗の分圧動作によって、信号 損失は6dBとなります。実効ソース抵抗も同じく1/2に減少しま したが、雑音寄与は $1/\sqrt{2}$  に、すなわち3dBしか減少していませ ん。したがって、雑音のないアンプ入力を仮定したときの正味の 理論的なSNRの劣化は3dBです。(実際には、アンプの雑音寄与 によって非終端時の雑音値も終端時の雑音値もともに劣化するの で、両者の差はいくぶん小さくなります。)

図5に、アクティブ・フィードバックを使用したアンプを示します。この図は、従来の反転アンプと非常によく似ています。しかし、ここでのゲイン、A "は非常に大きな開ループ・オペアンプ・ゲインではなく、LNP自体の比較的低い制御されたゲインであるため、分析は多少異なります。結果として、アンプの反転ピンにおけるインピーダンスは、有限な値だけ小さくなります。これは、式(3)に示されるよく知られた関係で求められます。

$$R_{IN} = \frac{R_F}{(1+A)}$$

(3)

ここでR<sub>F</sub>は帰還抵抗(各チャンネルでLNP<sub>IN</sub>PピンとFBピンの間に外部接続される)、Aはユーザーが選択したLNPのゲイン、R<sub>IN</sub>は結果として得られるアクティブ・フィードバックのアンプ入力インピーダンスです。この場合、上記の従来型終端とは異なり、信号電圧とR<sub>S</sub>雑音の両方が同じく1/2に(6dB)減衰されてから、"A"ゲイン設定で再増幅されます。これによって、上で説明した平方根効果による余分な3dBの劣化が避けられます。これはアクティブ終端技法の主要な利点です。

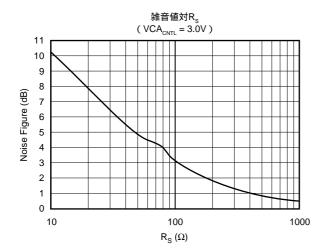

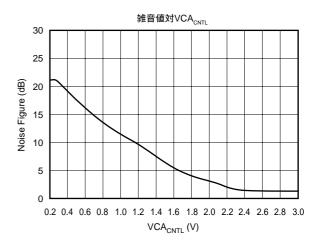

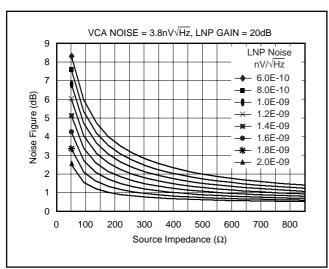

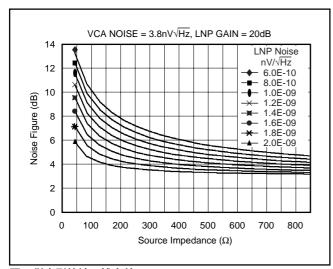

上で述べたように、前の説明ではLNP自体の入力雑音寄与を無視していました。また、完全に正確な分析には帰還抵抗の雑音寄与を含める必要があります。図6および図7に示される曲線によって、VCA2612のユーザーはアクティブ終端と従来の終端方法で達成可能な雑音値を比較することができます。各グラフの左端にあ

図5. アクティブ・フィードバックおよび従来のケーブル終端による構成

図6. アクティブ終端の雑音値

図7. 従来型終端の雑音値

るデータ点は、標準の50Ωケーブル終端での結果を示しています。これは最悪の雑音値を示すものですが、アクティブ・フィードバック法で得られる最大の効果を示すものでもあります。

ピン45のFBSW<sub>CNTL</sub>で制御されるスイッチによって、ユーザーはLNP<sub>IN</sub>PピンとSWFBピンの間に並列成分を追加することで帰還抵抗を小さくできます。2つの異なる帰還抵抗の値によって、2つの異なるアクティブ・フィードバック入力抵抗の値が得られます。したがって、アクティブ・フィードバック・インピーダンスは2つの異なるLNPゲイン設定で最適化できます。スイッチはLNPのバッファリングされた出力に接続され、オン抵抗は約1Ωです。

アクティブ・フィードバックを使用する場合、ユーザーは低周波での不安定性と過負荷の問題を注意して避ける必要があります。図8に、各種の低周波時定数を示します。再び式(3)の入力抵抗の計算を参照し、ゲイン項'A'が3.6kHz以下では低下することを考慮すると、実効LNP入力インピーダンスが3.6kHz以下では上昇する(約 $R_F$ のDC制限で)ことが明らかです。低周波での帰還極/ゼロとの相互作用を避け、インピーダンス特性の増加による信号レベルの上昇を防ぐために、外部 $R_F$ C $_C$ 時定数を約 $5\mu$ sに設定することを推奨します。

従来のオペアンプ回路構造では、最良のアクティブ・フィードバック・アーキテクチャを実現するのは困難です。帰還ループを閉じるには全体のゲイン、A が負でなければならず、低い電流雑音と高いゲイン精度を維持するには入力インピーダンスが高くなければなりません。しかし、電圧雑音性能を維持するには、非常に低い値の抵抗でゲイン比を設定する必要があります。2アンプ構成(高インピーダンス用の非反転アンプと負帰還用の反転アンプ)を使用すると、ループを閉じたときに余分な位相遅延と安定性の問題が発生します。VCA2612は、特許取得済みのアーキテクチャを使用してこれらの条件を満たし、低い消費電力、および入力と出力の両方における差動信号処理という新たな利点も提供します。

柔軟性を最大にして雑音を最小にするために、ユーザーはLNP の周波数応答を調整することができます。各チャンネルの COMP1およびCOMP2ピン(チャンネルAはピン10および11、

図8. 低周波LNP時定数

チャンネルBはピン26および27 )は、図4のQ3およびQ8のドレインにそれぞれ対応します。これらのピン間にコンデンサを配置することで、1極のローパス応答が得られ、"RC '時定数の実効' R " は約186 $\Omega$ になります。

#### LNP出力パッファ

差動LNP出力は、低インピーダンス負荷のドライブ用に設計された広帯域クラスAB電圧フォロワによってパッファリングされます。これは、VCA入力では入力インピーダンスがゲインに依存するため、LNPゲイン精度を保持するために必要です。また、このパッファは、LNP出力を取り出して外部フィルタやその他の信号処理回路をドライブする場合にも有用です。良好な歪性能は、135Ω以上のパッファ負荷で維持されます。前に述べたように、パッファ入力は3.6kHzのハイパス特性でLNP出力にAC結合され、DC同相モード・レベルはVCA入力とのマッチングのために正確なV<sub>CM</sub>で保持されます。

#### 電圧制御減衰器(VCA) 詳細

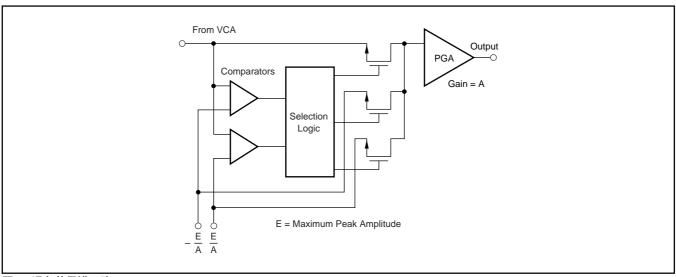

VCAは、"dBリニア"な減衰特性が得られるように設計されて います。すなわち、 $VCA_{CNTL}$ 制御電圧が同じ値だけ増加したとき のdBのゲイン損失は一定です。図9に、VCAのブロック図を示し ます。減衰器は本質的に、1つの直列入力抵抗R。と10個の同一の シャントFETによって構成される可変分圧器です。このFETは並 列に配置され、連続的にアクティブになるクリッピング・アンプ によって制御されます。各クリッピング・アンプは、"ソフト"な 伝達特性と十分に制御された出力制限電圧を持つ特化された電圧 コンパレータと考えることができます。リファレンス電圧1/1~ V10は、0Vから3.0Vまでの制御電圧レンジ内で等間隔に並んでい ます。各クリッピング・アンプの入力レンジ内で制御電圧が上昇 すると、アンプ出力はOV(FETが完全にオン)からV<sub>CM</sub> - V<sub>x</sub>(FET がほぼオフ)に上昇します。ここで、∨ 、 はコモン・ソース電圧、 ∨,はFETのしきい値電圧です。各FETがオフ状態に近づき、制御 電圧が上昇を続けると、次のクリッピング・アンプとFETが区分 的にリニアな減衰特性の次の部分を引き継ぎます。これにより、

低い制御電圧ではほとんどのFETがオンになり、高い制御電圧ではほとんどのFETがオフになります。各FETは、 $R_s$ と並列FET回路によって形成される分圧回路のシャント抵抗を下げる働きをします。

減衰器は2つの部分からなり、それぞれ5つの並列クリッピング・アンプとFETが含まれます。特別なリファレンス回路によって、(V<sub>CM</sub>-V<sub>T</sub>)制限電圧が温度およびICプロセスの変動に追従し、減衰器の制御特性への影響が最小限になるようにしています。

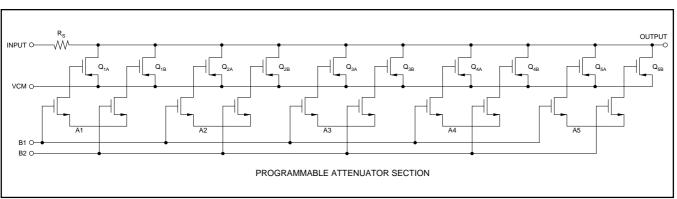

アナログ $VCA_{CNTL}$ ゲイン設定入力に加えて、減衰器アーキテクチャには3つのMGS(最大ゲイン設定)ピットによる8段階のデジタル・プログラム調整機能が備えられています。これは可能な最大ゲイン( $VCA_{CNTL}=3.0$ VでのVCAの最小減衰に対応)を3dB間隔で調整します。この機能は、図9に示す $Q1\sim Q10$ のFETシャント要素のそれぞれに対して複数のFETサブ要素を提供することで実現されています。図10の概略図において、各シャントFETは2つのサブ要素 $Q_{NA}$ および $Q_{NB}$ として示されています。MGSピットによってドライブされる選択スイッチは、このサブ要素FETの両方または一方をアクティブにして、最大 $R_{ON}$ を調整し、それによって段階的な減衰オプションを実現します。

VCAは差動信号またはシングルエンド信号の処理に使用できます。完全な差動動作では、フルスケール信号に対して約10dBだけ2次高調波歪が低減されます。

VCAの入力インピーダンスはゲイン設定によって変化します。 これは、プログラマブル分圧構造の抵抗が変化するためです。減 衰係数が大きい(すなわちゲイン設定が低い)と、インピーダンス は約135Ωの直列抵抗値に近づきます。

LNP段と同様に、VCA出力はPGAにAC結合されます。これは、減衰に依存するDC同相電圧がPGAに波及しないため、PGAのDC出力レベルが一定に保たれることを意味します。

最後に、VCA<sub>CNTL</sub>入力はFETゲート入力によって構成されることに注意してください。これにより非常に高いインピーダンスが得られ、複数のVCA2612デバイスを負荷への大きな影響なしに並列接続できるようになります。

図10. プログラマブル減衰器部

図9. 対数制御特性への区分的近似

#### 過負荷復帰回路 詳細

70dBの最大全体ゲインを持つVCA2612は、信号の過負荷の影響を受けやすくなっています。そのような状況は、さまざまなゲインおよび減衰設定によってLNPとPGAのいずれでも生じる可能性があります。LNPは、シンゲルエンドで1Vp-p(差動で2Vp-p)までの低歪出力を生成するように設計されています。したがって、リニアな動作のための最大入力信号は、2Vp-pをLNPの差動ゲイン設定値で割った大きさになります。LNP内のクランプ回路によって、それ以上の入力振幅における対称なクリッピングと短い復帰時間が保証されます。VCA自体は、基本的に分圧器であるため、本質的に過負荷状況は発生しません。ただし、PGAポストアンプは、高いゲイン設定では特に、突然の過負荷に対して脆弱です。超音波画像処理など多くの信号処理アプリケーションにおい

て、高速な過負荷復帰は必須条件です。PGAの入力には、範囲外信号を検出する特別なコンパレータ回路が備えられています(検出レベルはPGAゲイン設定に依存します)。信号がコンパレータの入力しきい値を超えると、VCA出力がブロックされ、適切な固定DCレベルで置き換えられます。これにより、高速でクリーンな過負荷復帰が実現されます。基本的なアーキテクチャを図11に示します。この回路では、範囲の上と下の両方の範囲外状況が検出され、修正されます。

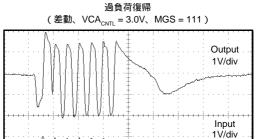

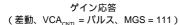

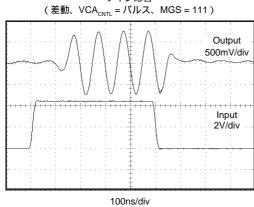

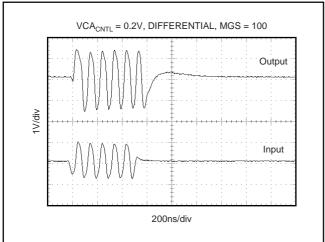

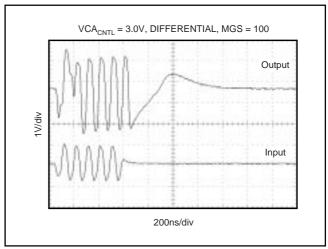

図12および図13に、それぞれVCA・PCAの最小ゲイン(0dB)および最大ゲイン(36dB)に対するMGS=100での標準的な過負荷復帰波形を示します。どちらの場合も、LNPゲインは25dBに設定されています。

図11. 過負荷保護回路

図12. 最小ゲインでの過負荷復帰応答

図13. 最大ゲインでの過負荷復帰応答

#### PGAポストアンプ 詳細

図14に、PGAブロックの概略回路図を示します。前に述べたように、PGAゲインはVCAの最大減衰係数を制御するのと同じMGSピットによってプログラムされます。具体的には、各MGS設定でのPGAゲインは、その設定でのVCAの最大減衰の逆数です。したがって、VCA・PGAの全体ゲインは、アナログVCA<sub>CNTL</sub>入力が0V(=最大減衰)に設定されると、常に0dB(ユニティ)になります。VCA<sub>CNTL</sub>=3V(減衰なし)の場合は、VCA・PGAゲインは

| MGS <b>設定</b> | VCA <b>ゲイン最小~最大、</b><br>VCA <sub>CNTL</sub> = 0V~3V | 差動PGA<br>ゲイン | VCA・PGA <b>ゲイン</b><br>最小~最大 |

|---------------|-----------------------------------------------------|--------------|-----------------------------|

| 000           | -24dB to 0dB                                        | 24dB         | 0dB to 24dB                 |

| 001           | -27dB to 0dB                                        | 27dB         | 0dB to 27dB                 |

| 010           | -30dB to 0dB                                        | 30dB         | 0dB to 30dB                 |

| 011           | -33dB to 0dB                                        | 33dB         | 0dB to 33dB                 |

| 100           | -36dB to 0dB                                        | 36dB         | 0dB to 36dB                 |

| 101           | -39dB to 0dB                                        | 39dB         | 0dB to 39dB                 |

| 110           | -42dB to 0dB                                        | 42dB         | 0dB to 42dB                 |

| 101           | -45dB to 0dB                                        | 45dB         | 0dB to 45dB                 |

表 . MGS設定

プログラムされたPGAゲイン(24dBから45dBまで3dB**間隔)**によって制御されます。

これを明確にするために、ゲインと減衰係数の詳細を表 に示します。

PGAアーキテクチャは、差動プログラマブル・ゲイン電圧/電流コンパータ段と、それに続く、差動出力の各側を作成してパッファリングするトランスインピーダンス・アンプによって構成されています。電圧/電流コンパータに関連する回路は、LNPの項で示した回路と似ていますが、LNPでの固定抵抗回路の代わりに、選択可能なPGAゲイン設定抵抗のコンピネーション(MGSピットによって制御される)が8つ追加されています。PGA設計のもう1つの要件として、入力雑音は低くなければなりません。これは、LNPとPGAの間に大きな信号減衰を挿入可能であるためです。最小のVCA減衰(小さな入力信号に対して使用される)においては、LNP雑音が支配的です。最大のVCA減衰(大きな入力信号)においては、PGA雑音が支配的です。PGA出力がシングルエンドで使用された場合、見かけのゲインは6dB低くなることに注意してください。

**図**14. PGA**の概略ブロック図**

#### 外観

20 ©BBJ000503K