# 16 ビット、クワッド、電圧出力、シリアル入力 D/Aコンバータ

### 特長

● 低消費電力: 200mW

● ユニポーラまたはバイポーラ動作

単一電源出力範囲:+10∨両電源出力範囲:±10∨

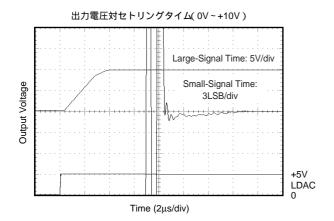

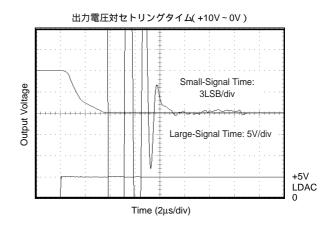

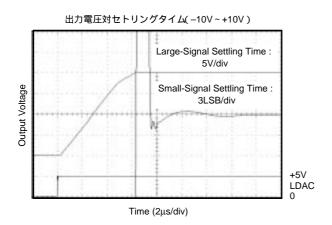

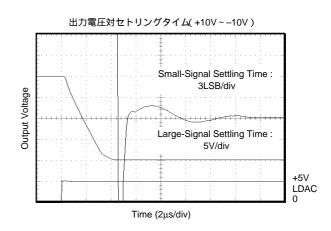

● セトリングタイム: 10µs(0.003%まで)

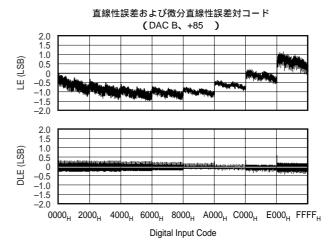

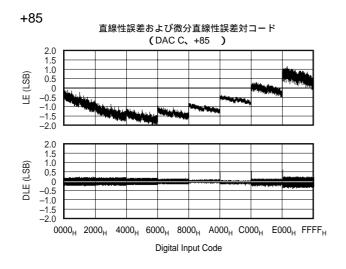

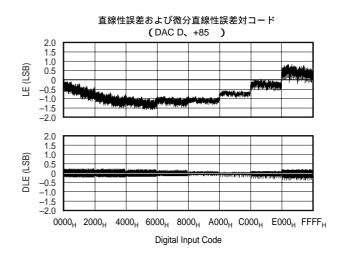

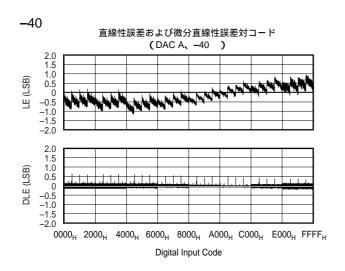

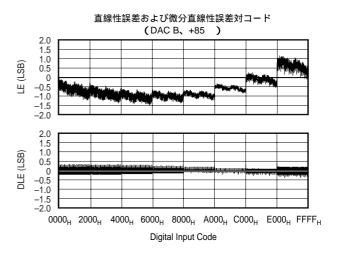

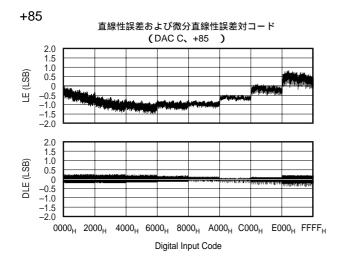

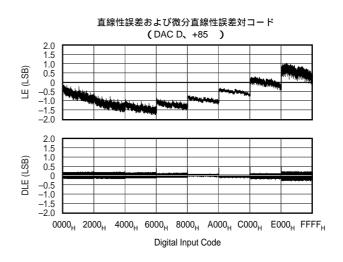

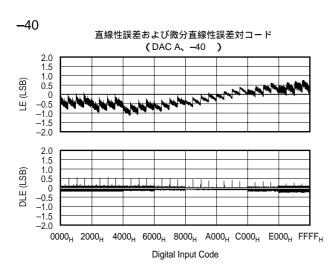

● 単調性:16ビット(-40 ~+85 )

● プログラマブル・リセット:ミッドスケール またはゼロスケール

● ダブル・バッファ方式のデータ入力

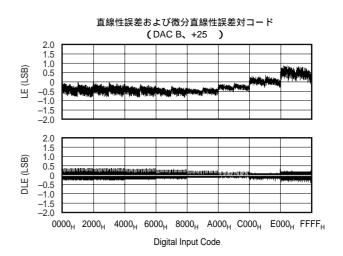

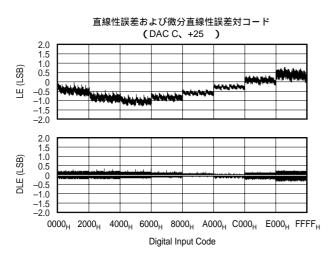

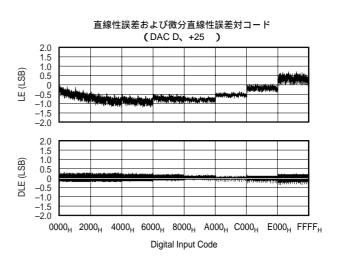

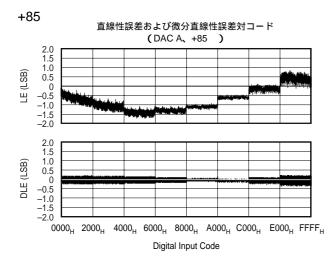

• DNL:  $\pm 1$ LSB(-40 ~+85 )

### アプリケーション

- プロセス制御

- 自動試験装置のピン・エレクトロニクス

- 閉ループ・サーボ制御

- モータ制御

- データ・アクイジション・システム

- DAC-PER-PINプログラマ

### 概要

DAC7734は、仕様温度範囲にわたり16ビットの単調性が保証されたクワッド・タイプの16ビット電圧出力D/Aコンパータです。24ビットのシリアルデータ入力、全てのDACの同時更新が可能なダブル・パッファ方式のDAC入力ロジック、複数のDACをデイジーチェーン接続できるシリアルデータ出力を備えています。非同期のプログラマブル・リセット機能は、全てのレジスタをミッドスケール(8000<sub>H</sub>)またはゼロスケール(0000<sub>H</sub>)コードに設定します。DAC7734は、+15Vの単一電源または+15V、-15V、+5Vの電源で動作します。

小型かつ低消費電力のDAC7734は、自動試験装置、DAC-PER-PINプログラマ、データ・アクイジション・システム、閉ループ・サーボ制御に理想的です。パッケージは、48ピンSSOPで供給され、-40 から+85 の温度範囲で仕様が保証されています。

### 仕様(両電源)

特に記述のない限り、 $T_A = T_{MIN} \sim T_{MAX}$ 、 $V_{CC} = +15$ V、 $V_{DD} = +5$ V、 $V_{SS} = -15$ V、 $V_{REF}H = +10$ V、 $V_{REF}L = -10$ Vです。

|                                                                                                                            |                                                  |                                                  | DAC7734                                        | E                                                      | С       | AC7734E       | В        | С     | AC7734E         | С         |                                  |

|----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--------------------------------------------------|------------------------------------------------|--------------------------------------------------------|---------|---------------|----------|-------|-----------------|-----------|----------------------------------|

| パラメータ                                                                                                                      | 条件                                               | 最小                                               | 標準                                             | 最大                                                     | 最小      | 標準            | 最大       | 最小    | 標準              | 最大        | 単位                               |

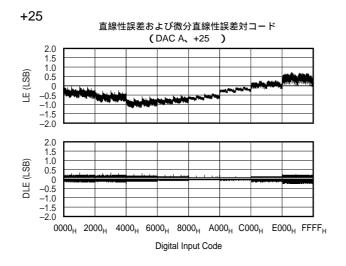

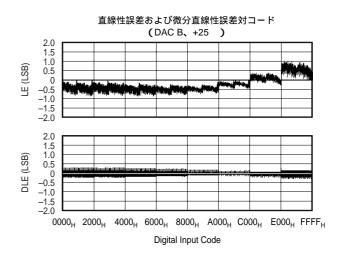

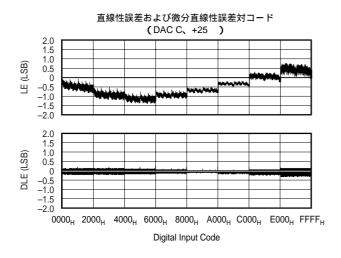

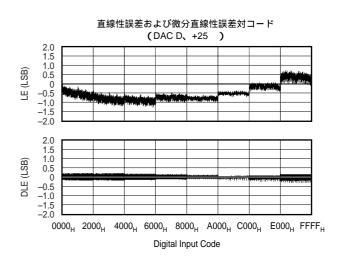

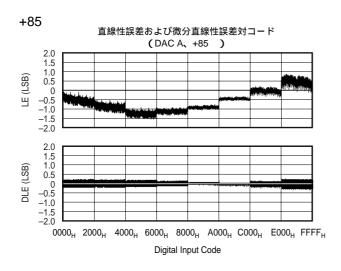

| 精度<br>直線性誤差(INL)<br>T <sub>MIN</sub> ~T <sub>MAX</sub><br>直線性のマッチ                                                          | T = 25                                           |                                                  | ±4                                             | ±3<br>±4                                               |         | *             | *        |       | ±2              | ±2<br>±3  | LSB<br>LSB<br>LSB                |

| 微分直線性誤差(DNL)<br>T <sub>MIN</sub> ~T <sub>MAX</sub><br>単調性、T <sub>MIN</sub> ~T <sub>MAX</sub><br>パイポーラ・ゼロ誤差                 | T = 25                                           | 14                                               |                                                | ±3<br>±3                                               | 15      |               | ±2<br>±2 | 16    |                 | ±1<br>±1  | LSB<br>LSB<br>Bit                |

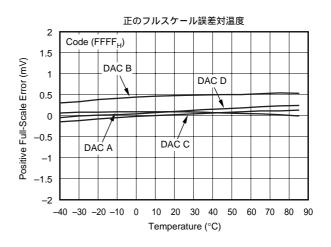

| バイポーラ・ゼロ誤差<br>バイポーラ・ゼロ誤差、T <sub>MIN</sub> ~T <sub>MAX</sub><br>フルスケール誤差                                                    | T = 25                                           |                                                  | ±0.01                                          | ±0.025<br>±0.05<br>±0.025                              |         |               | * *      |       |                 | * * *     | % of FSR<br>% of FSR<br>% of FSR |

| フルスケール誤差、T <sub>MIN</sub> ~T <sub>MAX</sub><br>バイポーラ・ゼロのマッチング                                                              | チャンネル間の<br>マッチング                                 |                                                  |                                                | ±0.05<br>±0.024                                        |         |               | *        |       |                 | *         | % of FSR<br>% of FSR             |

| フルスケールのマッチング                                                                                                               | チャンネル間の<br>マッチング                                 |                                                  |                                                | ±0.024                                                 |         |               | *        |       |                 | *         | % of FSR                         |

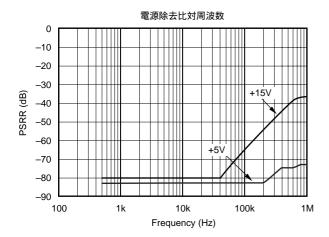

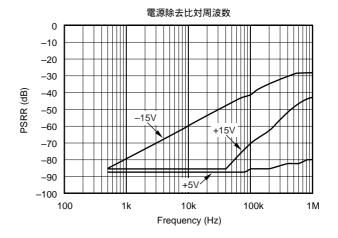

| 電源除去比(PSRR)                                                                                                                | フルスケール                                           |                                                  |                                                | 25                                                     |         |               | *        |       |                 | *         | ppm/V                            |

| アナログ出力<br>電圧出力<br>出力電流<br>最大負荷キャパシタンス<br>短絡電流<br>短絡時間                                                                      | V <sub>ss</sub> 、V <sub>cc</sub> またはGND          | V <sub>REF</sub> L<br>±5                         | 500<br>±20<br>無制限                              | V <sub>REF</sub> H                                     | *       | * *           | *        | *     | * *             | *         | V<br>mA<br>pF<br>mA              |

| リファレンス入力<br>高電位リファレンス入力電圧範囲<br>低電位リファレンス入力電圧範囲<br>高電位リファレンス入力電流<br>低電位リファレンス入力電流                                           | SS CC-W-I                                        | V <sub>REF</sub> L + 1.25<br>-10<br>-0.3<br>-3.2 |                                                | +10<br>V <sub>REF</sub> H - 1.25<br>2.6<br>-0.3        | * * * * |               | * * *    | * * * |                 | * * * * * | V<br>V<br>mA<br>mA               |

| <b>ダイナミック特性</b><br>セトリングタイム                                                                                                | ±0.003%まで、<br>20V出力ステップ                          |                                                  | 9                                              | 11                                                     |         | *             | *        |       | *               | *         | μs                               |

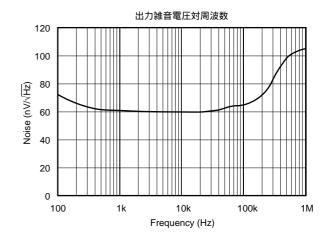

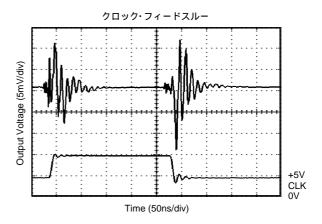

| チャンネル間クロストーク<br>デジタル・フィードスルー<br>出力雑音電圧                                                                                     | 図5参照<br>f = 10kHz                                |                                                  | 0.5<br>2<br>60                                 |                                                        |         | * *           |          |       | * *             |           | LSB<br>nV-s<br>nV/√ Hz           |

| デジタル入力<br>V <sub>IH</sub><br>V <sub>IL</sub><br>I <sub>IH</sub><br>I <sub>IL</sub>                                         |                                                  | 0.7 • V <sub>DD</sub>                            |                                                | V <sub>DD</sub><br>0.3 • V <sub>DD</sub><br>±10<br>±10 | *       |               | * *      | *     |                 |           | V<br>V<br>μΑ<br>μΑ               |

| デジタル出力<br>V <sub>OH</sub><br>V <sub>OL</sub>                                                                               | $I_{OH} = -0.8\text{mA}$ $I_{OL} = 1.6\text{mA}$ | 3.6                                              | 4.5<br>0.3                                     | 0.4                                                    | *       | *             | *        | *     | *               | *         | V<br>V                           |

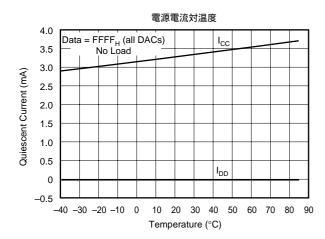

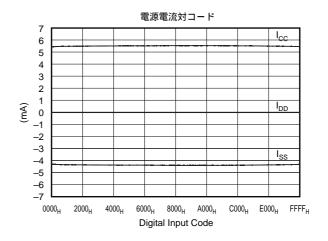

| 電源<br>V <sub>DD</sub><br>V <sub>CC</sub><br>V <sub>SS</sub><br>I <sub>DD</sub><br>I <sub>CC</sub><br>I <sub>SS</sub><br>電力 |                                                  | +4.75<br>+14.25<br>-14.25                        | +5.0<br>+15.0<br>-15.0<br>50<br>6<br>-5<br>170 | +5.25<br>+15.75<br>-15.75                              | * *     | * * * * * * * | * * *    | * *   | * * * * * * * * | * *       | V<br>V<br>V<br>μA<br>mA<br>mA    |

| <b>温度範囲</b><br>仕様に規定された性能                                                                                                  |                                                  | -40                                              |                                                | +85                                                    | *       |               | *        | *     |                 | *         |                                  |

<sup>\*</sup> 印は、DAC7734Eのグレードと同じ値であることを示します。

このデータシートに記載されている情報は、信頼しうるものと考えておりますが、不正確な情報や記載漏れ等に関して弊社は責任を負うものではありません。情報の使用について弊社は責任を負えませんので、各ユーザーの責任において御使用下さい。価格や仕様は予告なしに変更される場合がありますのでご了承下さい。ここに記載されているいかなる回路についても工業所有権その他の権利またはその実施権を付与したり承諾したりするものではありません。弊社は弊社製品を生命維持に関する機器またはシステムに使用することを承認しまたは保証するものではありません。

### 仕様(単一電源)

特に記述のない限り、 $T_A = T_{MIN} \sim T_{MAX}$ 、 $V_{CC} = +15V$ 、 $V_{DD} = +5V$ 、 $V_{SS} = GND$ 、 $V_{REF}H = +10V$ 、 $V_{REF}L = +50 \text{mV}$ です。

|                                                                                                                              |                                                     | 1                                              | DAC7734I                              | E                                                      | D       | AC7734E     | В        | D     | AC7734E     | С        |                               |

|------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------|------------------------------------------------|---------------------------------------|--------------------------------------------------------|---------|-------------|----------|-------|-------------|----------|-------------------------------|

| パラメータ                                                                                                                        | 条件                                                  | 最小                                             | 標準                                    | 最大                                                     | 最小      | 標準          | 最大       | 最小    | 標準          | 最大       | 単位                            |

| 精度<br>直線性誤差 <sup>(1)</sup> (INL)<br>T ~ T                                                                                    | T = 25                                              |                                                |                                       | ±3<br>±4                                               |         |             | *        |       |             | ±2<br>±3 | LSB<br>LSB                    |

| T <sub>MIN</sub> ~T <sub>MAX</sub><br>直線性のマッチ<br>微分直線性誤差(DNL)                                                                | T = 25                                              |                                                | ±4                                    | ±3<br>±3                                               |         | *           | ±2<br>±2 |       | ±2          | ±1<br>±1 | LSB<br>LSB<br>LSB             |

| T <sub>MIN</sub> ~ T <sub>MAX</sub><br>単調性、T <sub>MIN</sub> ~ T <sub>MAX</sub><br>ユニポーラ・ゼロ誤差                                 | T = 25                                              | 14                                             | ±0.01                                 | ±0.025                                                 | 15      |             | *        | 16    |             | *        | Bit<br>% of FSR<br>% of FSR   |

| ユニポーラ・ゼロ誤差、T <sub>MIN</sub> ~ T <sub>MAX</sub><br>フルスケール誤差<br>フルスケール誤差、T <sub>MIN</sub> ~ T <sub>MAX</sub><br>ユニポーラ・ゼロのマッチング | T = 25                                              |                                                |                                       | ±0.05<br>±0.025<br>±0.05                               |         |             | *        |       |             | *        | % of FSR<br>% of FSR          |

| ユニボーラ・ゼロのマッチング<br> <br> <br>  フルスケールのマッチング                                                                                   | チャンネル間の<br>マッチング<br>チャンネル間の                         |                                                |                                       | ±0.024<br>±0.024                                       |         |             | *        |       |             | *        | % of FSR                      |

| 電源除去比(PSRR)                                                                                                                  | マッチング<br>フルスケール                                     |                                                |                                       | 25                                                     |         |             | *        |       |             | *        | ppm/V                         |

| <b>アナログ出力</b><br>電圧出力                                                                                                        | $V_{REF}L = 0V, V_{SS} = 0V$ $R = 10k\Omega$        | 0                                              |                                       | V <sub>REF</sub> H                                     | *       |             | *        | *     |             | *        | V                             |

| 出力電流<br>最大負荷キャパシタンス<br>短絡電流<br>短絡時間                                                                                          | V <sub>cc</sub> またはGND                              | ±5                                             | 500<br>±20<br>無制限                     |                                                        | *       | * *         |          | *     | * *         |          | mA<br>pF<br>mA                |

| リファレンス入力<br>高電位リファレンス入力電圧範囲<br>低電位リファレンス入力電圧範囲<br>高電位リファレンス入力電流<br>低電位リファレンス入力電流                                             |                                                     | V <sub>REF</sub> L + 1.25<br>0<br>-0.3<br>-1.5 |                                       | +10<br>V <sub>REF</sub> H - 1.25<br>1.0<br>-0.3        | * * * * |             | * * *    | * * * |             | * * *    | V<br>V<br>mA<br>mA            |

| <b>ダイナミック特性</b><br>セトリングタイム                                                                                                  | ±0.003%まで、<br>10V出力ステップ                             |                                                | 8                                     | 10                                                     |         | *           | *        |       | *           | *        | μs                            |

| チャンネル間クロストーク<br>デジタル・フィードスルー<br>出力雑音電圧                                                                                       | 図6参照<br>f = 10kHz                                   |                                                | 0.5<br>2<br>60                        |                                                        |         | * *         |          |       | * *         |          | LSB<br>nV-s<br>nV/√Hz         |

| デジタル入力<br>V <sub>IH</sub><br>I <sub>IL</sub>                                                                                 |                                                     | 0.7 • V <sub>DD</sub>                          |                                       | V <sub>DD</sub><br>0.3 • V <sub>DD</sub><br>±10<br>±10 | *       |             | * *      | *     |             |          | V<br>V<br>μΑ<br>μΑ            |

| デジタル出力<br>V <sub>OH</sub><br>V <sub>OL</sub>                                                                                 | I <sub>OH</sub> = -0.8mA<br>I <sub>OL</sub> = 1.6mA | 3.6                                            | 4.5<br>0.3                            | 0.4                                                    | *       | *           | *        | *     | *           | *        | V                             |

| 電源<br>V <sub>DD</sub><br>V <sub>CC</sub><br>V <sub>SS</sub><br>I <sub>DD</sub><br>I <sub>CC</sub> 電力                         |                                                     | +4.75<br>+14.25                                | +5.0<br>+15.5<br>0<br>50<br>3.5<br>50 | +5.25<br>+15.75                                        | *       | * * * * * * | *        | *     | * * * * * * | *        | V<br>V<br>V<br>μA<br>mA<br>mW |

| <b>温度範囲</b><br>仕様に規定された性能                                                                                                    |                                                     | -40                                            |                                       | +85                                                    | *       |             | *        | *     |             | *        |                               |

<sup>\*</sup> 印は、DAC7734Eのグレードと同じ値であることを示します。

注:(1) $V_{SS}$  = 0Vの場合、ゼロスケール誤差が負になる可能性があるため、仕様は0021 $_{H}$ 以上のコードに適用されます。

### 絶対最大定格(1)

| V <sub>cc</sub> ~ V <sub>ss</sub>       | 0.3V ~ +32V                |

|-----------------------------------------|----------------------------|

| V <sub>cc</sub> ~ AGND                  | 0.3V ~ +16V                |

| V <sub>ss</sub> ~ AGND                  |                            |

| AĞND ~ DGND                             |                            |

| V <sub>RFF</sub> H ~ AGND               | –9V ~ +11V                 |

| VL ~ AGND                               | 11V ~ +9V                  |

| V <sub>DD</sub> ~ GND                   | 0.3V ~ +6V                 |

| V <sub>RFF</sub> H ~ V <sub>RFF</sub> L | 1V ~ 22V                   |

| デジタル入力電圧(対GND)                          | $-0.3$ V ~ $V_{DD}$ +0.3V  |

| デジタル出力電圧( 対GND )                        | $-0.3V \sim V_{DD} + 0.3V$ |

| 最大接合部温度                                 | +150                       |

| 動作温度範囲                                  | 40 ~+85                    |

| 保存温度範囲                                  | 65 ~ +150                  |

| リード温度( 10秒間の半田付け )                      | +300                       |

注:(1)定格を超えるオーバ・ストレスは、デバイスに永久的な損傷を与えます。絶対最大条件下に長時間置いた場合は、デバイスの信頼性が低下することがあります。

# X

### 静電気放電対策

静電気放電はわずかな性能の低下から完全なデバイスの故障に至るまで、様々な損傷を与えます。全ての集積回路は、適切なESD保護方法を用いて、取扱いと保存を行うようにして下さい。高精度の集積回路は、損傷に対して敏感であり、極めてわずかなパラメータの変化により、デバイスに規定された仕様に適合しなくなる場合があります。

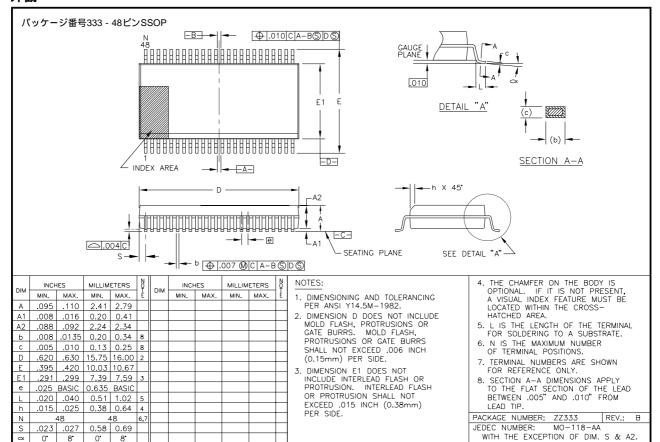

#### パッケージ情報/ご発注の手引き

| モデル       | 直線性誤差<br>(LSB) | 微分非直線性<br>(LSB) | パッケージ    | パッケージ図番号 | 仕様温度範囲                  | <b>発注番号</b> (1) | 供給時の状態 |

|-----------|----------------|-----------------|----------|----------|-------------------------|-----------------|--------|

| DAC7734E  | <u>±</u> 4     | ±3              | 48ピンSSOP | 333      | <b>−40</b> ~ <b>+85</b> | DAC7734E        | マガジン   |

| DAC7734E  | ±4             | ±3              | 48ピンSSOP | 333      | -40 ~ +85               | DAC7734E/1K     | テープリール |

| DAC7734EB | <u>±</u> 4     | <u>+2</u>       | 48ピンSSOP | 333      | <b>−40</b> ~ <b>+85</b> | DAC7734EB       | マガジン   |

| DAC7734EB | <u>±</u> 4     | <u>+2</u>       | 48ピンSSOP | 333      | <b>−40</b> ~ <b>+85</b> | DAC7734EB/1K    | テープリール |

| DAC7734EC | ±3             | ±1              | 48ピンSSOP | 333      | <b>−40</b> ~ <b>+85</b> | DAC7734EC       | マガジン   |

| DAC7734EC | ±3             | ±1              | 48ピンSSOP | 333      | <b>−40</b> ~ <b>+85</b> | DAC7734EC/1K    | テープリール |

注:(1)スラッシュ(/)が付記されたモデルは、表示数量のテープリールでのみ供給されます(例えば、/1Kはリール1本あたり1,000個入りであることを示します)。 "DAC7734E/1K "を発注すると、1,000個入りテープリール1本が納品されます。

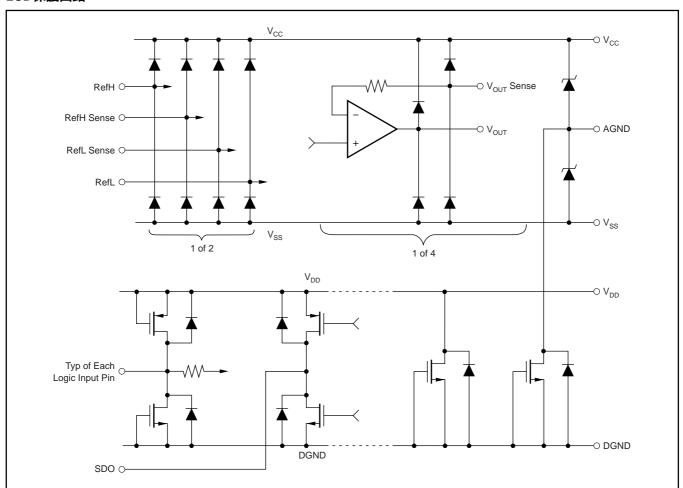

#### ESD保護回路

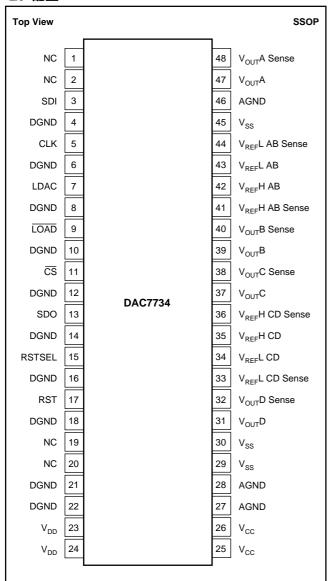

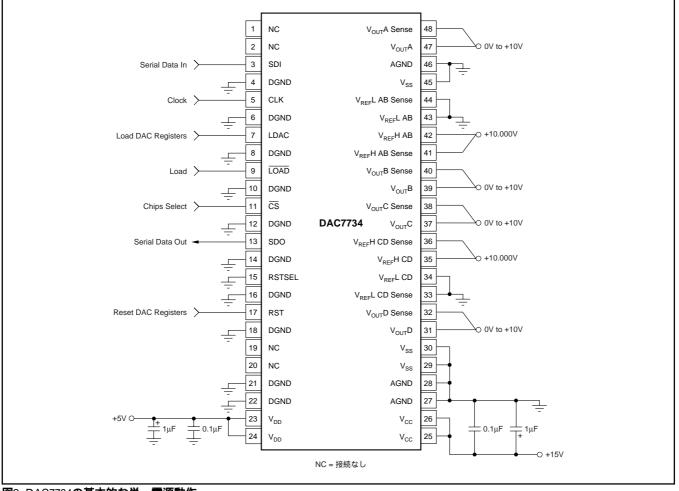

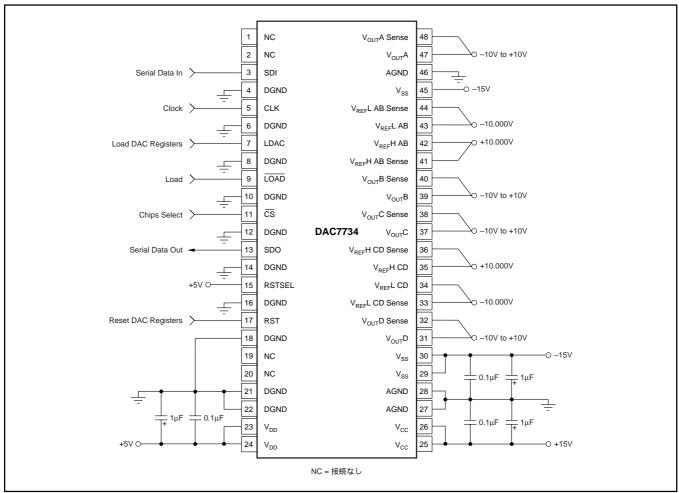

### ピン配置

### ピン構成

| _  | 一一                          |                                                                                                   |

|----|-----------------------------|---------------------------------------------------------------------------------------------------|

| ピン | 名称                          | 説明                                                                                                |

| 1  | NC                          | ノー・コネクション(オープン)                                                                                   |

| 2  | NC                          | ノー・コネクション(オープン)                                                                                   |

| 3  | SDI                         | シリアル・データ入力                                                                                        |

| 4  | DGND                        | デジタル・グランド                                                                                         |

| 5  | CLK                         | データ・クロック入力                                                                                        |

| 6  | DGND                        | デジタル・グランド                                                                                         |

| 7  | LDAC                        | ファッル・ファー  <br>  DACレジスタ・ロード制御。立ち上がリエッジ                                                            |

| ,  | LB/(O                       | でトリガする。                                                                                           |

| 8  | DGND                        | デジタル・グランド                                                                                         |

| 9  | LOAD                        | DAC入力レジスタ・ロード制御。アクティブ                                                                             |

| ŭ  | 20/12                       | " D – "。                                                                                          |

| 10 | DGND                        | デジタル・グランド                                                                                         |

| 11 | <del>cs</del>               | チップ・セレクト。アクティブ"ロー "。                                                                              |

| 12 | DGND                        | デジタル・グランド                                                                                         |

| 13 | SDO                         | シリアル・データ出力                                                                                        |

| 14 | DGND                        | デジタル・グランド                                                                                         |

| 15 | RSTSEL                      | リセット・セレクト。RSTの動作を決定する。                                                                            |

| 15 | KOTOLL                      | "ハイ"の場合、DACレジスタはRSTコマンドによってミッドスケー以 8000H )に設定される。<br>"ロー"の場合、DACレジスタはRSTコマンドによってゼロ(0000H )に設定される。 |

| 16 | DGND                        | デジタル・グランド                                                                                         |

| 17 | RST                         | リセット。立ち上がりエッジでトリガする。<br>                                                                          |

|    |                             | DACレジスタをRSTSELの状態に応じてミッド<br>スケールまたはゼロに設定する。                                                       |

| 18 | DGND                        | デジタル・グランド                                                                                         |

| 19 | NC                          | ノー・コネクション(オープン)                                                                                   |

| 20 | NC                          | ノー・コネクション(オープン)                                                                                   |

| 21 | DGND                        | デジタル・グランド                                                                                         |

| 22 | DGND                        | デジタル・グランド                                                                                         |

| 23 | V <sub>DD</sub>             | デジタル+5\電源                                                                                         |

| 24 | V <sub>DD</sub>             | デジタル+5\電源                                                                                         |

| 25 | V <sub>cc</sub>             | アナログ+15V電源                                                                                        |

| 26 | V <sub>cc</sub>             | アナログ+15V電源                                                                                        |

| 27 | AGND                        | アナログ・グランド                                                                                         |

| 28 | AGND                        | アナログ・グランド                                                                                         |

| 29 | V <sub>ss</sub>             | アナログ-15V電源または0V単一電源                                                                               |

| 30 |                             | アナログ-15V電源または0V単一電源                                                                               |

|    | V <sub>ss</sub>             |                                                                                                   |

| 31 | V <sub>OUT</sub> D          | DAC Dの出力電圧                                                                                        |

| 32 | V <sub>оит</sub> D Sense    | DAC Dの出力アンプの反転入力。帰還ループを<br>負荷で閉じるために使用する。                                                         |

| 33 | V <sub>REF</sub> L CD Sense | DAC CとDの低電位リファレンス・センス入力                                                                           |

| 34 | V <sub>REF</sub> L CD       | DAC CとDの低電位リファレンス入力                                                                               |

| 35 | $V_{REF}H$ CD               | DAC CとDの高電位リファレンス入力                                                                               |

| 36 | V <sub>REF</sub> H CD Sense | DAC CとDの高電位リファレンス・センス入力                                                                           |

| 37 | $V_{OUT}C$                  | DAC Cの出力電圧                                                                                        |

| 38 | V <sub>out</sub> C Sense    | DAC Cの出力アンプの反転入力。帰還ループを<br>負荷で閉じるために使用する。                                                         |

| 39 | $V_{OUT}B$                  | DAC Bの出力電圧                                                                                        |

| 40 | V <sub>оит</sub> B Sense    | DAC Bの出力アンプの反転入力。帰還ループを<br>負荷で閉じるために使用する。                                                         |

| 41 | V <sub>REF</sub> H AB Sense | DAC AとBの高電位リファレンス・センス入力                                                                           |

| 42 | V <sub>REF</sub> H AB       | DAC AとBの高電位リファレンス入力                                                                               |

| 43 | V <sub>REF</sub> L AB       | DAC AとBの低電位リファレンス入力                                                                               |

| 44 | V <sub>REF</sub> L AB Sense | DAC AとBの低電位リファレンス・センス入力                                                                           |

| 45 | V <sub>ss</sub>             | アナログ-15V電源または0V単一電源                                                                               |

| 46 | AGND                        | アナログ・グランド                                                                                         |

| 47 | V <sub>OUT</sub> A          | DAC Aの出力電圧                                                                                        |

| 48 | V <sub>оит</sub> A Sense    | DAC Aの出力アンプの反転入力。帰還ループを                                                                           |

|    | 001 2 300                   | 負荷で閉じるために使用する。                                                                                    |

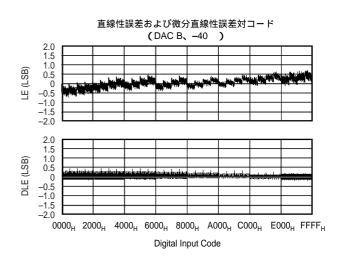

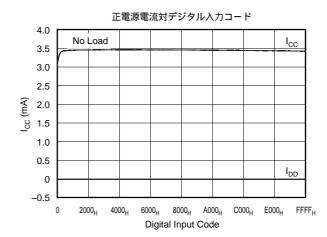

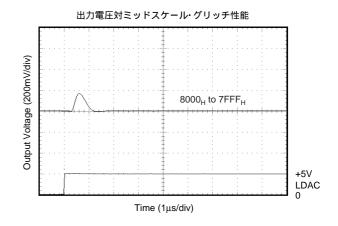

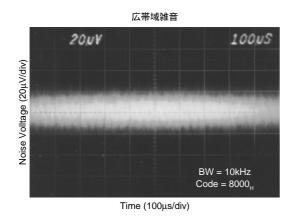

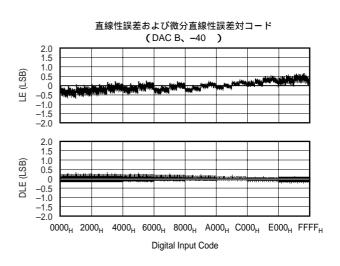

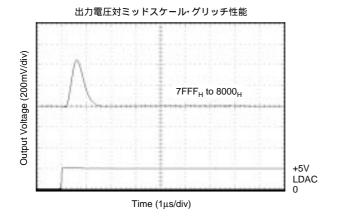

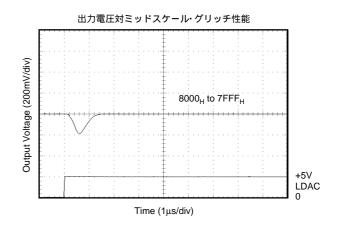

特に記述のない限り、 $T_{_A}$  = +25 、  $V_{_{DD}}$  = +5V、 $V_{_{CC}}$  = +15V、 $V_{_{SS}}$  = 0V、 $V_{_{REF}}$ H = +10V、 $V_{_{REF}}$ L = 0V、代表的ユニットです。

特に記述のない限り、 $T_{_A}$  = +25 、  $V_{_{DD}}$  = +5V、 $V_{_{CC}}$  = +15V、 $V_{_{SS}}$  = 0V、 $V_{_{REF}}$ H = +10V、 $V_{_{REF}}$ L = 0V、代表的ユニットです。

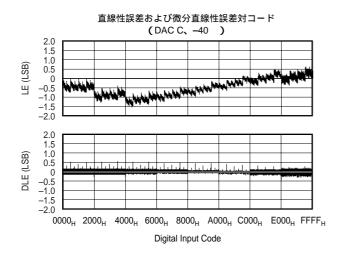

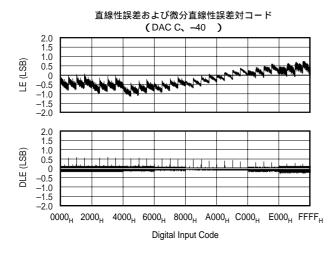

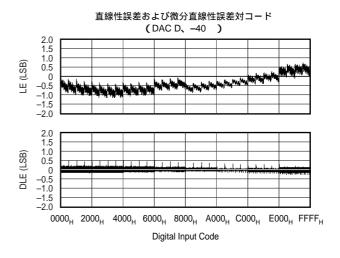

特に記述のない限り、 $T_{_A}$  = +25 、  $V_{_{DD}}$  = +5V、 $V_{_{CC}}$  = +15V、 $V_{_{SS}}$  = 0V、 $V_{_{REF}}$ H = +10V、 $V_{_{REF}}$ L = 0V、代表的ユニットです。

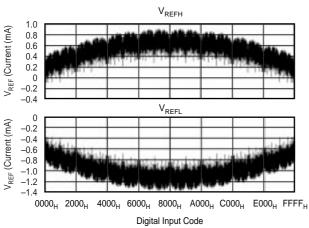

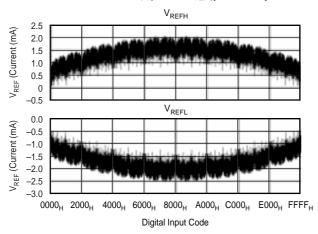

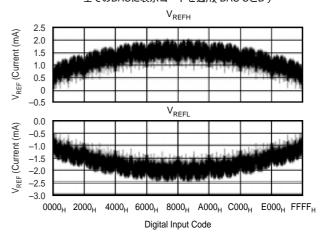

リファレンス電流対コード 全てのDACに表示コードを適用( DAC AとB )

リファレンス電流対コード 全てのDACに表示コードを適用( DAC CとD )

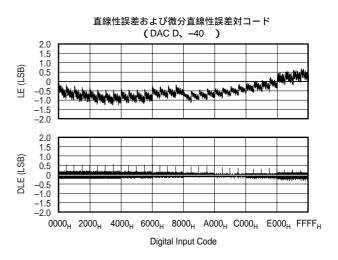

特に記述のない限り、 $T_{A}=+25$  、 $V_{DD}=+5V$ 、 $V_{CC}=+15V$ 、 $V_{SS}=0V$ 、 $V_{REF}H=+10V$ 、 $V_{REF}L=0V$ 、代表的ユニットです。

特に記述のない限り、 $T_{_A}$  = +25 、 $V_{_{DD}}$  = +5V、 $V_{_{CC}}$  = +15V、 $V_{_{SS}}$  = 0V、 $V_{_{REF}}$ H = +10V、 $V_{_{REF}}$ L = 0V、代表的ユニットです。

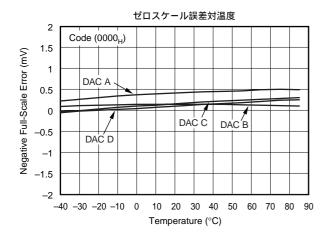

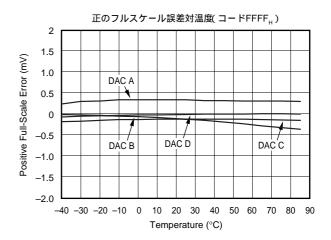

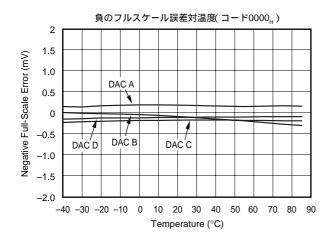

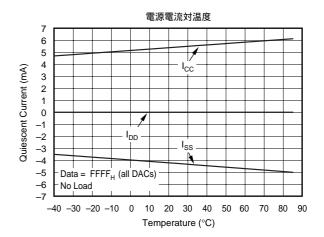

特に記述のない限り、 $T_{_A}$  = +25 、 $V_{_{DD}}$  = +5V、 $V_{_{CC}}$  = +15V、 $V_{_{SS}}$  = -15V、 $V_{_{REF}}$ H = +10V、 $V_{_{REF}}$ L = -10V、代表的ユニットです。

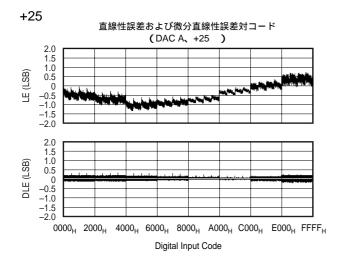

### **代表的性能曲線:**V<sub>ss</sub> = -15V

特に記述のない限り、 $T_A$  = +25 、 $V_{DD}$  = +5V、 $V_{CC}$  = +15V、 $V_{SS}$  = -15V、 $V_{REF}$ H = +10V、 $V_{REF}$ L = -10V、代表的ユニットです。

# **代表的性能曲線:**V<sub>ss</sub> = -15V

特に記述のない限り、 $T_{_A}$  = +25 、 $V_{_{DD}}$  = +5V、 $V_{_{CC}}$  = +15V、 $V_{_{SS}}$  = -15V、 $V_{_{REF}}$ H = +10V、 $V_{_{REF}}$ L = -10V、代表的ユニットです。

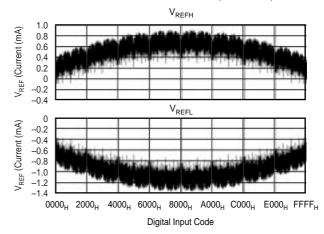

リファレンス電流対コード 全てのDACに表示コードを適用(DAC AとB)

リファレンス電流対コード 全てのDACに表示コードを適用(DAC CとD)

バイポーラ・ゼロスケール誤差対温度(コード8000<sub>H</sub>)

2

1.5

1 DAC A

0.5

E O DAC D DAC B DAC C

0 DAC D DAC D DAC B DAC C

0 DAC D DAC B DAC D DAC B DAC C

0 DAC D DAC B DAC D DAC B DAC C

0 DAC D DAC B DAC D DAC B DAC D DAC B DAC D DAC B DAC D DAC D DAC B DAC D DAC

特に記述のない限り、 $T_A$  = +25 、  $V_{DD}$  = +5V、 $V_{CC}$  = +15V、 $V_{SS}$  = -15V、 $V_{REF}$ H = +10V、 $V_{REF}$ L = -10V、代表的ユニットです。

# 代表的性能曲線: $V_{SS}=-15V$ 特に記述のない限り、 $T_{A}=+25$ 、 $V_{DD}=+5V$ 、 $V_{CC}=+15V$ 、 $V_{SS}=-15V$ 、 $V_{REF}H=+10V$ 、 $V_{REF}L=-10V$ 、代表的ユニットです。

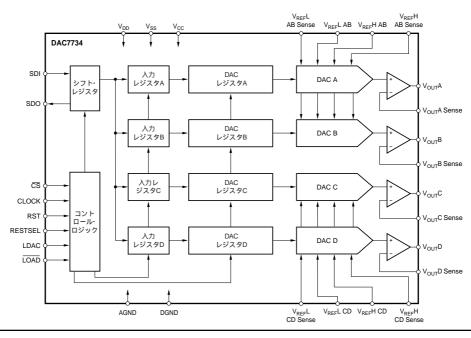

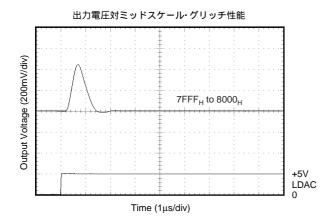

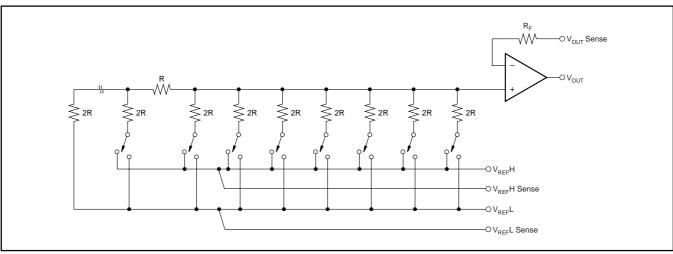

### 動作原理

DAC7734は、クワッド・タイプの16ビット電圧出力DACです。 アーキテクチャは、R-2Rラダー構成で、分割された3つのMSBと 後段にバッファとして機能するオペアンプがあります。各DACご とにR-2Rラダー・ネットワーク、分割されたMSB、出力オペアン プがあります(図1参照)。最小電圧出力(ゼロスケール)および最 大電圧出力(フルスケール)は、外部電圧リファレンスV<sub>REF</sub>Lおよ びV<sub>REF</sub>Hによって設定します。 デジタル入力は、4つのDACのいずれかを選択する2ビットのアドレス・コード、1ビットのクイック・ロード・ビット、未使用の5ビット、および16ビットのDACコード(MSBファースト)からなる24ビットのシリアル・ワードです。コンパータは、+15Vの単一電源または±15Vの両電源および+5Vのロジック電源で動作させることができ、全てのDACの出力電圧およびDACレジスタを直ちにミッドスケール(コード8000円)またはゼロスケール(コード0000円)に設定するリセット機能を備えています。DAC7734の基本動作については図2および3を参照して下さい。

図1. DAC7734のアーキテクチャ

図2. DAC7734の基本的な単一電源動作

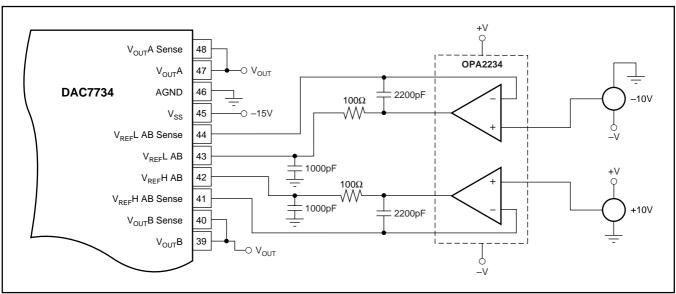

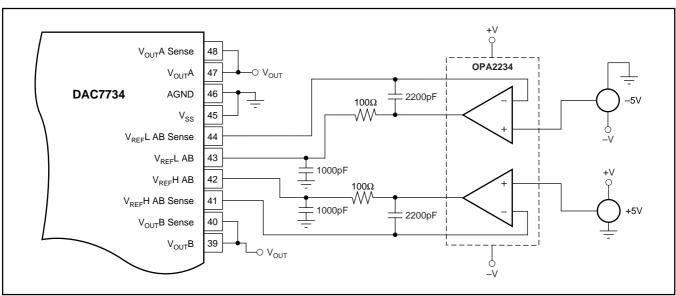

図3. DAC7734の基本的な両電源動作

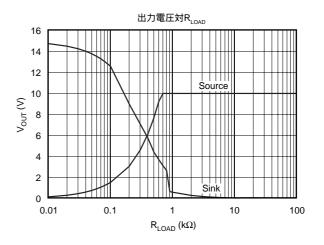

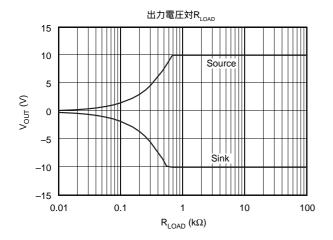

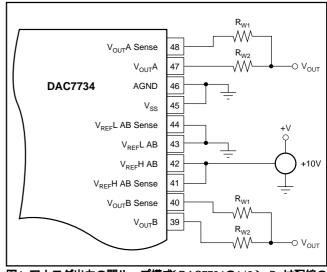

#### アナログ出力

$V_{\rm ss}=-15$ V( 両電源動作)のとき、出力アンプは電源レールの4V 以内までスイングでき、-40 ~+85 の温度範囲にわたり保証されています。 $V_{\rm ss}=0$ V( 単一電源動作)で $R_{\rm LOAD}$ もグランドに接続しているとき、出力はグランドまでスイングできます。 $V_{\rm ss}=0$ Vのときは、ゼロスケール誤差の測定にも注意が必要です。出力アンプのオフセットが負の場合、出力電圧はグランド以下にスイングできないため、最初のいくつかのデジタル入力コード(0000<sub>H</sub>、0001<sub>H</sub>、0002<sub>H</sub>など)で出力電圧が変化しないことがあります。負の制限値の-5mVの場合、最初の仕様出力はコード0021<sub>H</sub>から始まります。

D/Aコンパータは高精度なため、接地や接触抵抗などのシステム設計の問題が非常に重要になります。フルスケール・レンジが  $10 \lor 0$ 16 ビット・コンパータでは、1 LSBの値は $152 \mu \lor$  になります。負荷電流が1 mAの場合、わずか $150 m\Omega$ の配線およびコネクタの直列抵抗( $R_{w2}$ 、図4参照)によって $150 \mu \lor$  の電圧降下が発生します。システム・レイアウトの観点からは、標準的な1オンス銅箔プリント基板の面積当たりの抵抗が $0.5 m\Omega$ であることから、負荷が1 mAの場合、幅 $20 \le 1$  インチ、長さ6インチのプリント基板のパターンで $150 \mu \lor$  の電圧降下が発生することになります。

DAC7734では、高開ループ・ゲインの出力アンプのフォースおよびセンスの出力構成を使用できます。この機能によって出力アンプのループを負荷で閉じ(図4参照)、高精度な出力電圧を確保できます。

**図**4. アナログ出力の閉ループ構成 DAC7734の1/2 )。R<sub>w</sub>は配線の 抵抗を示す。

#### リファレンス入力

リファレンス入力 $V_{REF}$ Lおよび $V_{REF}$ Hは、 $V_{REF}$ Hが $V_{REF}$ Lより 1.25V以上高い限り、 $V_{SS}$  + 4Vから $V_{CC}$  - 4Vまでの任意の電圧を使用することができます。各DACの最小出力は、 $V_{REF}$ L+わずかなオフセット電圧(ほぼ出力オペアンプのオフセット)に等しくなります。最大出力は、 $V_{REF}$ H+同様のオフセット電圧に等しくなります。 $V_{SS}$ (負電源)は、グランドに接続するか、-14.25Vから-15.75Vの範囲に保たなければならないことに注意して下さい。 $V_{SS}$ の電圧は、コンバータ内部の複数のバイアス・ポイントを設定します。 $V_{SS}$ が上記の2つの構成のいずれでもない場合、バイアス値が不正になり、デバイスの正しい動作が保証されません。

V<sub>REE</sub>Hに流れ込みV<sub>REE</sub>Lから流れ出る電流は、DACの出力電圧

に依存し、数マイクロアンペアから約2.0ミリアンペアまでの範囲で変動します。リファレンス入力は、リファレンスに対して変動する負荷として作用します。DAC7734は、変動するリファレンス電流や回路インピーダンスによって発生する内部誤差を最小限に抑えることができるリファレンスのドライブおよびセンス端子を備えています。図5から図9に、各種のリファレンスの構成と、直線性および微分直線性への影響を示します。

最初にアナログ電源をオンにする必要があります。 $\lor_{cc} \lor_{cs} \lor_{cs}$ を同時にオンにしない場合は、最初に $\lor_{ss}$ をオンする必要があります。最初にリファレンス電源をオンにした場合、 $\lor_{cc}$ および $\lor_{ss}$ 電源がESD保護ダイオードを介してリファレンスから供給されます(4ページ参照)。

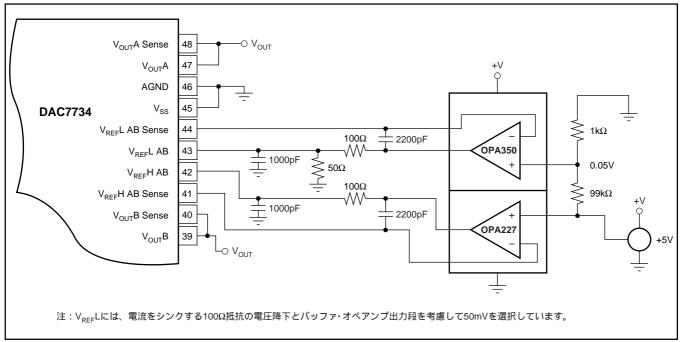

図5. 両電源の性能曲線に使用したパッファ付きリファレンスの構成( DAC7734の1/2 )

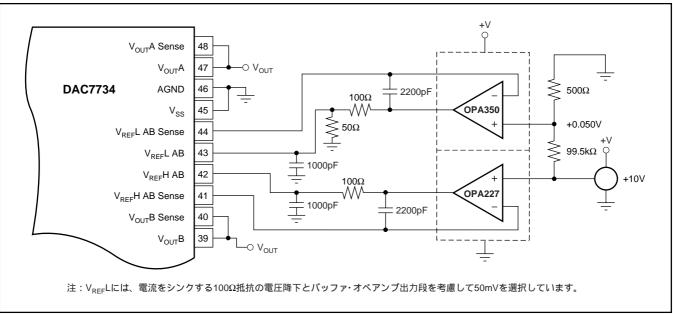

図6. 単一電源の性能曲線に使用した低電位リファレンスが50mVのバッファ付きリファレンス(DAC7734の1/2)

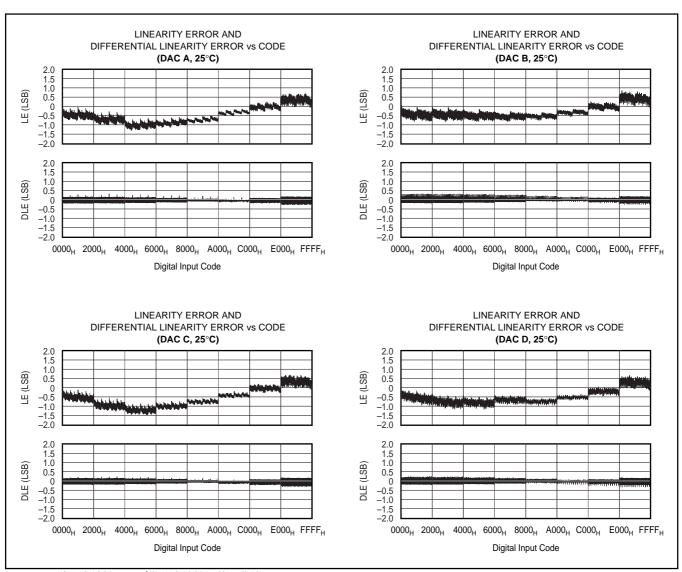

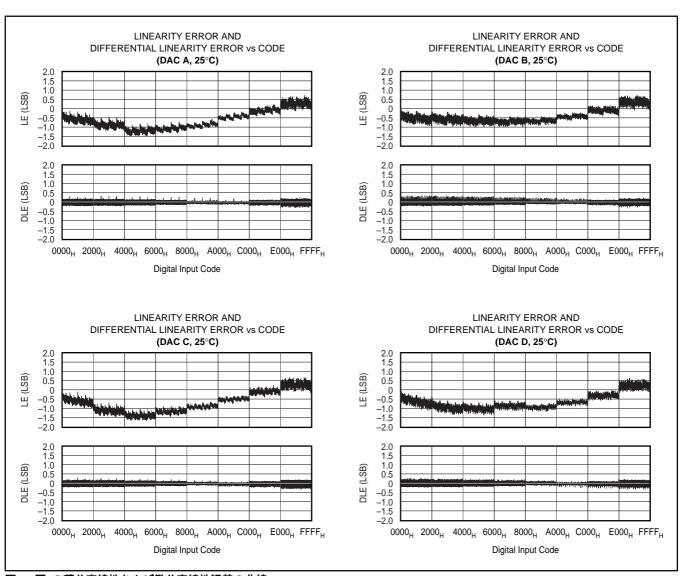

図7. 図8の積分直線性および微分直線性誤差の曲線

図8. V<sub>REF</sub>L = -5V、V<sub>REF</sub>H = +5V**の両電源パッファ付きリファレンス(** DAC7734**の**1/2 **)**

**図**9. V<sub>REF</sub>L = 50mV、V<sub>REF</sub>H = +5V**の単一電源パッファ付きリファレンス**

図10. 図9の積分直線性および微分直線性誤差の曲線

#### デジタル・インターフェース

表にDAC7734の基本的なコントロール・ロジックを示します。インターフェースは、データ・クロック(CLK)入力、シリアルデータ(SDI)、DAC入力レジスタ・ロード制御信号(LOAC)から構成されます。また、複数のシリアル・デバイスのシリアル通信を可能にするチップ・セレクト(CS)入力もあります。非同期リセット(RST)入力は、その立ち上がりエッジで起動時や周期的リセットまたは緊急リセット時の状態を既知の値に戻します。この値はリセット・セレクト(RSTSEL)信号の状態によって決まります。

DACコード、クイック・ロード制御、およびアドレスは、24 ビットのシリアル・インターフェースで転送されます(表 参照)。シフト・レジスタにシフト・インされる最初の2ビット(B23、B22)は、DACレジスタ・アドレスで、LOADが ロー でなったときに更新される入力レジスタを選択します。3番目のビット(B21)は クイック・ロード ピットです。このビットがハイで場合、アドレス・ビット(B23、B22)の状態にかかわらず、LOAD信号がローでなったとき、シフト・レジスタのコードが全てのDAC入力レジスタにロードされます。"クイック・ロード"ビットがローでの場合、シフト・レジスタのコードは指定されたDAC入力レジスタだけにロードされます。ピットB20からB16は未使用で、論理値は不定です。最後の16ビット(B15からB0)は、選択した入力レジスタにロードされるDACコード(LSBファースト)です。

内部のDACレジスタは、レベル・トリガではなくエッジ・トリガで動作します。LDAC信号がローでから、ハイで温移すると、DAC入力レジスタにあるデジタル・ワードがラッチされます。一段目のレジスタ(DAC入力レジスタ)は、LOAD信号でレベル・トリガされます。このダブル・バッファ方式のアーキテクチャは、アナログ出力に影響することなく各DACに新しいデータを入力できるように設計されています。新しいデータがデバイスに入力さ

れたら、LDACの立ち上がリエッジによって全てのDAC出力を同時に更新できます。また、DAC入力レジスタに任意の時点で書き込みを行い、トリガ信号(LDAC)によってDAC出力電圧を同時に変更することもできます。

CSおよびCLKはORゲートで結合され、シリアル・ツー・パラレル・シフト・レジスタを制御することに注意して下さい。この2つの入力は、相互に交換が可能です。また、シリアル転送の最後ででSを、ハイでにするときのCLKの状態にも注意する必要があります。CSを、ハイでしたときにCLKがローでの場合、ORゲートから立ち上がりエッジがシフト・レジスタに送られ、さらに1ビット内部データがシフトします。この結果、データが不正になり、誤った入力レジスタが選択される可能性があります。CSおよびCLKの両方を使用する場合は、CLKがハイでときのみCSを、ハイですることが必要です。一方だけ使用する場合は、CSまたはCLKのどちらでもシフト・レジスタを動作させることができます。詳細については、表を参照して下さい。

| CS <sup>(1)</sup> | CLK <sup>(1)</sup> | LOAD             | RST | シリアル・シフト・レジスタ |

|-------------------|--------------------|------------------|-----|---------------|

| H <sup>(2)</sup>  | X <sup>(3)</sup>   | Н                | Н   | 変化しない         |

| L <sup>(4)</sup>  | L                  | Н                | Н   | 変化しない         |

| L                 | (5)                | Н                | Н   | 1ビット進む        |

|                   | L                  | Н                | Н   | 1ビット進む        |

| H <sup>(6)</sup>  | Х                  | L <sup>(7)</sup> | Н   | 変化しない         |

| H <sup>(6)</sup>  | X                  | Н                | (8) | 変化しない         |

注:(1  $\overline{\text{CS}}$ およびCLKは、相互に交換が可能です。(2  $\overline{\text{H}}$  =  $\overline{\text{DI}}$  =  $\overline{\text{DI}}$  9.7 "  $\overline{\text{H}}$  7" (3  $\overline{\text{X}}$  =  $\overline{\text{H}}$  8.6 (4  $\overline{\text{X}}$  =  $\overline{\text{DI}}$  9.7 "  $\overline{\text{DI}}$  9.7 "  $\overline{\text{DI}}$  9.7 "  $\overline{\text{DI}}$  9.7 "  $\overline{\text{DI}}$  9.8 "  $\overline{\text{DI}}$  9.9 "  $\overline{$

#### 表 シリアル・シフト・レジスタの真理値表

#### シリアルデータ入力

| B23 | B22 | B21          | B20 | B19 | B18 | B17 | B16 | B15 | B14 | B13 | B12 | B11 | B10 | В9 | B8 | В7 | B6 | B5 | В4 | ВЗ | B2 | B1 | В0 |

|-----|-----|--------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|

| A1  | A0  | クイック・<br>ロード | Х   | Х   | Х   | Х   | Х   | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

| A1                         | A0                    | cs                    | RST       | RSTSEL                     | LDAC                  | LOAD                  | 入力レジスタ                                                     | DAC <b>レジスタ</b>                                                    | モード                                                                               | DAC             |

|----------------------------|-----------------------|-----------------------|-----------|----------------------------|-----------------------|-----------------------|------------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------------------------------------------------------|-----------------|

| L<br>H<br>H<br>X<br>X<br>X | L<br>H<br>X<br>X<br>X | L<br>L<br>H<br>H<br>X | H H H H H | X<br>X<br>X<br>X<br>X<br>L | X<br>X<br>X<br>H<br>X | L<br>L<br>H<br>H<br>X | 書き込み<br>書き込み<br>書き込み<br>まさルド<br>ホールド<br>ゼロにスケールに<br>ミットセット | ホールド<br>ホールド<br>ホールド<br>ホールド<br>書きル<br>ボーにリセット<br>ゼロドスケールに<br>リセット | 書き込み入力<br>書き込み入力<br>書き込み入力<br>書き込み入力<br>更新<br>ホールド<br>ゼロにリセット<br>ミッドスケールに<br>リセット | A B C D 全 全 全 全 |

表 DAC7734のロジックの真理値表

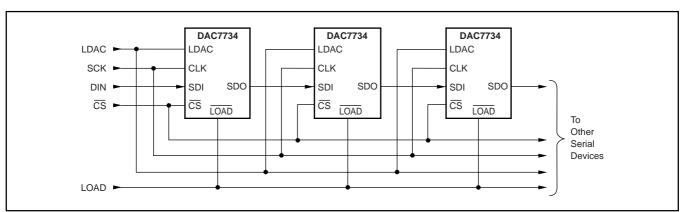

#### シリアルデータ出力

シリアルデータ出力(SDO)は、内部シフト・レジスタの出力です。DAC7734のSDOはドライブされた出力で、外部のプルアップは不要です。DAC7734は、各デバイスのSDOピンを次のデバイスのSDIピンに接続することにより、いくつでもデイジーチェーン接続することができます(図11参照)。

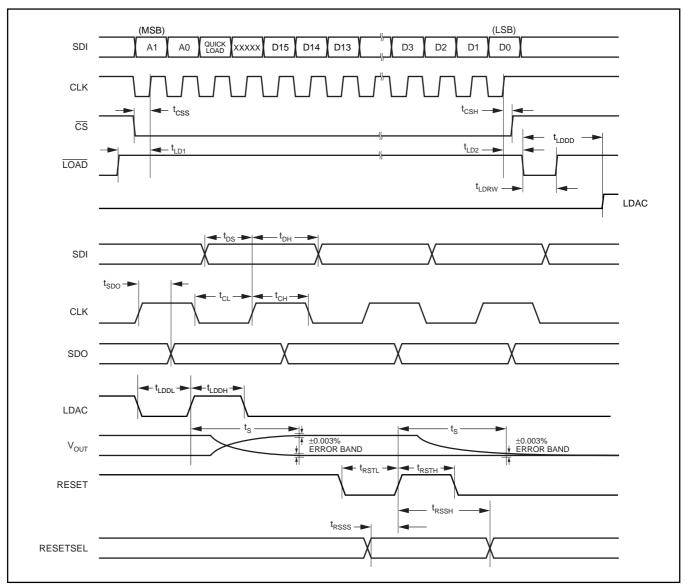

#### デジタルのタイミング

図12および表 は、DAC7734のデジタル・インターフェースの タイミングを表しています。

#### デジタル入力のコーディング

DAC7734**の入力データは、ストレート・バイナリ・フォーマットです。**出力電圧は式1で求められます。

$$V_{OUT} = V_{REF}L + \frac{(V_{REF}H - V_{REF}L) \cdot N}{65,536}$$

(1)

ここで、Nはデジタル入力コードです。この式には、オフセット(ゼロスケール)またはゲイン(フルスケール)誤差の影響は含まれていません。

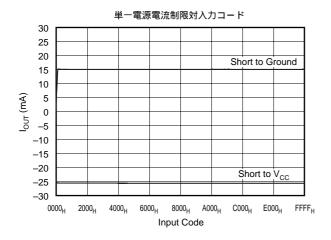

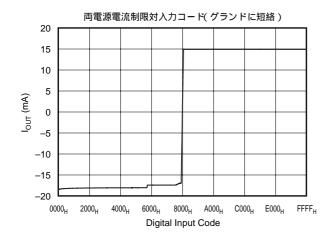

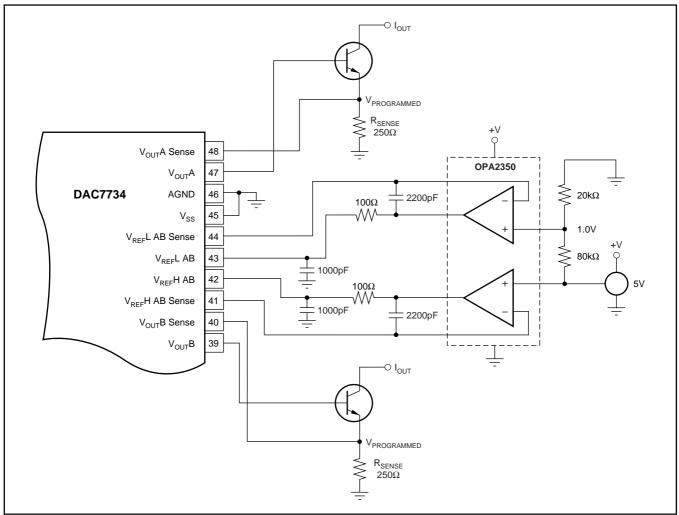

#### デジタル制御のプログラマブル電流ソース

DAC7734は、プログラマブル電流ソースなどのアプリケーション回路の設計に広い柔軟性をもたせるユニークな機能を備えています。DAC7734では出力アンプの開ループ構成と差動リファレンス入力の両方を利用できます。出力アンプの開ループ構成によりループ内にトランジスタを配置してデジタル制御の単方向電流ソースを実現し、差動リファレンスによりフルスケール電流とゼロスケール電流の両方をプログラムすることができます。出力電流は次のように計算されます。

$$I_{OUT} = \left( \left( \frac{(V_{REF}H - V_{REF}L)}{R_{SENSE}} \right) \bullet \left( \frac{N}{65,536} \right) \right) + (V_{REF}L/R_{SENSE})$$

図13にDAC7734の4mAから20mAの電流出力構成を示します。 出力電流は式3によって計算されます。

$$I_{OUT} = \left( \left( \frac{5V - 1V}{250\Omega} \right) \bullet \left( \frac{N}{65,536} \right) \right) + \left( \frac{1V}{250\Omega} \right)$$

(3)

フルスケールの出力電流は16mAとゼロ電流の4mAの合計です。ゼロスケールの出力電流は4mA( $1\text{V}/250\Omega$ )のオフセット電流です。

図11. DAC7734のデイジーチェーン接続

| 記号                | 説明                                   | 最小  | 最大                  | 単位 |

|-------------------|--------------------------------------|-----|---------------------|----|

| t <sub>DS</sub>   | データ有効からCLKの立ち上がりまで                   | 10  |                     | ns |

| t <sub>DH</sub>   | CLK立ち上がり後のデータ有効保持                    | 20  |                     | ns |

| t <sub>CH</sub>   | CLK" ハイ "                            | 25  |                     | ns |

| t <sub>CL</sub>   | CLK" □ – "                           | 25  |                     | ns |

| t <sub>css</sub>  | CS" ロー "からCLKの立ち上がりまで                | 15  |                     | ns |

| t <sub>csh</sub>  | CLK" ハイ "から <del>CS</del> の立ち上がりまで   | 0   |                     | ns |

| t <sub>LD1</sub>  | LOAD" ハイ "からCLKの立ち上がりまで              | 10  |                     | ns |

| t <sub>LD2</sub>  | CLKの立ち上がりから <del>LOAD</del> " ロー "まで | 30  |                     | ns |

| t <sub>LDRW</sub> | LOAD" □ ー "時間                        | 30  |                     | ns |

| t <sub>LDDL</sub> | LDAC" ロー "時間                         | 40  |                     | ns |

| t <sub>LDDH</sub> | LDAC" 八イ "時間                         | 40  |                     | ns |

| t <sub>spo</sub>  | SDO伝搬遅延                              | 10  | 45                  | ns |

| t <sub>RSSS</sub> | RESETSEL有効からRESET" ハイ "まで            | 0   |                     | ns |

| t <sub>RSSH</sub> | RESET" ハイ "からRESETSEL無効まで            | 100 |                     | ns |

| t <sub>RSTL</sub> | RESET" ロー "時間                        | 10  |                     | ns |

| t <sub>RSTH</sub> | RESET" 八イ "時間                        | 10  |                     | ns |

| t <sub>LDDD</sub> | LOAD" ロー "からLDACの立ち上がりまで             | 40  |                     | ns |

| t <sub>s</sub>    | セトリングタイム                             |     | 11( 両電源 )10( 単一電源 ) | μs |

表 . タイミング仕様(T<sub>4</sub> = -40 ~+85 )

図12. デジタル入出力のタイミング

図13. デジタル制御の4~20mAの電流ソース(DAC7734の1/2)

#### 外観

25 ©BBJ000303K