## DAC7724 DAC7725

## 12**ビット、クワッド、電圧出力** D/A**コンバータ**

### 特長

- 低消費電力: 250mW(最大)

- **単一電源出力レンジ:**+10∨

- デュアル電源出力レンジ:±10V

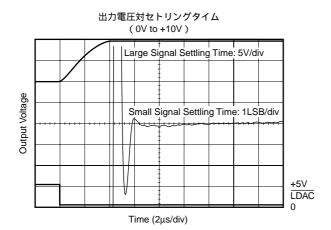

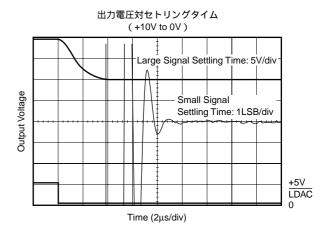

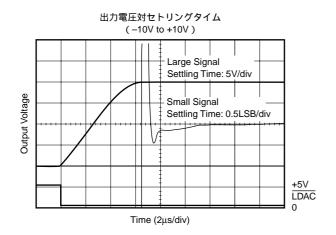

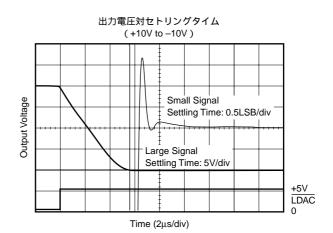

- セトリングタイム: 10µs(0.012%まで)

- 直線性および単調性: 12ビット(-40 ~+85 )

- ミッドスケール( DAC7724 )または ゼロスケール( DAC7725 )にリセット

- データ・リードバック

- データ入力のダブル・バッファリング

### アプリケーション

- プロセス制御

- 閉ループ・サーボ制御

- モータ制御

- データ・アクイジション・システム

### 概要

DAC7724およびDAC7725は、仕様温度範囲にわたり12 ビットの単調性が保証された12ビット、クワッド・タイプの電圧出力D/Aコンバータです。データ入力は12ビット並列で、ダブル・バッファリングDAC入力ロジック(全DACの同時更新が可能)および内部入力レジスタのリードバック・モードを備えています。非同期リセット機能により、すべてのレジスタがミッドスケール・コードの800点(DAC7724)またはゼロスケールの000点(DAC7725)にクリアされます。DAC7724およびDAC7725は、+15Vの単一電源、または+15Vと-15Vのデュアル電源で動作できます。

各DACの消費電力が低くサイズも小さいため、DAC7724 およびDAC7725は、自動試験装置、DAC PER PINプログ ラマ、データ・アクイジション・システム、閉ループ・サー ボ制御に理想的です。DAC7724およびDAC7725のパッケー ジは28ピンPLCCまたは28ピンSOPで供給され、-40 ~ +85 の温度範囲で保証されています。

PDSJ-1517B February, 2000

### 仕様:デュアル電源

特に記述のない限り、 $T_{_A} = -40$  ~+85 、 $V_{_{CC}} = +15$ V、 $V_{_{DD}} = +5$ V、 $V_{_{SS}} = -15$ V、 $V_{_{REFH}} = +10$ V、 $V_{_{REFL}} = -10$ Vです。

|                                                                                                                                                                              |                                                                                                                                               |                                                 | AC7724N,<br>AC7725N, |                                                        |                  | C7724NB,<br>C7725NB, |                                     |                                                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|----------------------|--------------------------------------------------------|------------------|----------------------|-------------------------------------|------------------------------------------------|

| パラメータ                                                                                                                                                                        | 条件                                                                                                                                            | 最小                                              | 標準                   | 最大                                                     | 最小               | 標準                   | 最大                                  | 単位                                             |

| 精度<br>直線性誤差<br>直線性マッチング <sup>(2)</sup><br>微分直線性誤差<br>単調性<br>ゼロスケール・ドリフト<br>ゼロスケール・マッチング <sup>(2)</sup><br>フルスケール・マッチング <sup>(2)</sup><br>フルスケール・マッチング <sup>(2)</sup><br>電源感度 | T <sub>MIN</sub> ~T <sub>MAX</sub><br>コード = 000 <sub>H</sub><br>コード = FFF <sub>H</sub><br>フルスケール時                                             | 12                                              | 1 10                 | ±2<br>±2<br>±1<br>±2<br>±2<br>±2<br>±2                 | *                | *                    | ±1<br>±1<br>±1<br>*<br>*<br>±1<br>* | LSB(1) LSB LSB Bits LSB ppm/ LSB LSB LSB ppm/V |

| アナログ出力<br>電圧出力 <sup>(3)</sup><br>出力電流<br>負荷キャパシタンス<br>短絡電流<br>短絡時間                                                                                                           | 発振なし<br>対V <sub>ss</sub> 、V <sub>cc</sub> 、またはGND                                                                                             | V <sub>REFL</sub><br>±5                         | 500<br>±20<br>無制限    | $V_{REFH}$                                             | *                | * *                  | *                                   | V<br>mA<br>pF<br>mA                            |

| <b>リファレンス入力</b><br>V <sub>REFI</sub> 入力レンジ<br>V <sub>REFL</sub> 入力レンジ<br>Ref "ハイ" 入力電流<br>Ref "ロー" 入力電流                                                                      |                                                                                                                                               | V <sub>REFL</sub> + 1.25<br>-10<br>-0.5<br>-3.5 |                      | +10<br>V <sub>REFH</sub> - 1.25<br>3.0<br>0            | * * *            |                      | * * *                               | V<br>V<br>mA<br>mA                             |

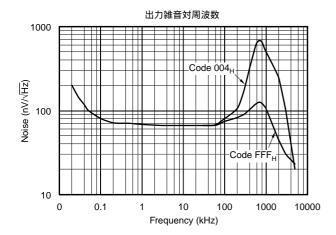

| ダイナミック性能<br>セトリングタイム<br>チャンネル間クロストーク<br>デジタル・フィードスルー<br>出力雑音電圧                                                                                                               | ±0.012%まで、20V出力ステップ<br>フルスケール・ ステップ<br>f = 10kHz                                                                                              |                                                 | 8<br>0.25<br>2<br>65 | 10                                                     |                  | * *                  | *                                   | μs<br>LSB<br>nV-s<br>nV/√Hz                    |

| デジタル入出力<br>ロジック・ファミリ<br>ロジック・レベル<br>V <sub>IH</sub><br>V <sub>OH</sub><br>V <sub>OH</sub><br>V <sub>OL</sub><br>データ・フォーマット                                                   | $\begin{split} I_{_{IH}} & \leq \pm 10 \mu A \\ I_{_{IL}} & \leq \pm 10 \mu A \\ I_{_{OH}} & = -0.8 m A \\ I_{_{OL}} & = 1.6 m A \end{split}$ | 2.4<br>-0.3<br>3.6<br>0.0                       | コンパチブル               | V <sub>DD</sub> + 0.3<br>0.8<br>V <sub>DD</sub><br>0.4 | *<br>*<br>*<br>* |                      | * * *                               | ><br>><br>>                                    |

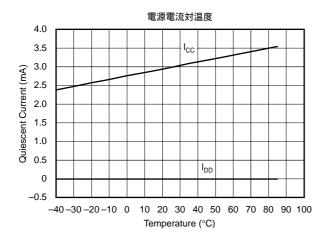

| 電源条件<br>V <sub>DD</sub><br>V <sub>CC</sub><br>V <sub>SS</sub><br>I <sub>DD</sub><br>I <sub>CC</sub><br>I <sub>SS</sub><br>消費電力                                               |                                                                                                                                               | +4.75<br>+14.25<br>-14.25                       | 50<br>6<br>-6<br>180 | +5.25<br>+15.75<br>-15.75<br>8.5                       | * * *            | * * *                | * * * *                             | V<br>V<br>V<br>μA<br>mA<br>mA                  |

| <b>温度範囲</b><br>仕様に規定された性能                                                                                                                                                    |                                                                                                                                               | -40                                             |                      | +85                                                    | *                |                      | *                                   |                                                |

<sup>\*</sup> 印はDAC7724/25N、Uと同じであることを示します。

注:(1)LSBは最下位ビットを意味します。 $V_{\text{REFL}}$  = +10V、 $V_{\text{REFL}}$  = -10Vの場合、1LSBは4.88mVです。(2)すべてのDAC出力は、仕様に規定された誤差の範囲内でマッチします。(3)ゼロスケール誤差およびフルスケール誤差を含まない理想的な出力電圧です。

このデータシートに記載されている情報は、信頼し得るものと考えておりますが、不正確な情報や記載漏れ等に関して弊社は責任を負うものではありません。情報の使用について弊社は責任を負えませんので、各ユーザーの責任において御使用下さい。価格や仕様は予告なしに変更される場合がありますのでご了承下さい。ここに記載されているいかなる回路についても工業所有権その他の権利またはその実施権を付与したり承諾したりするものではありません。弊社は弊社製品を生命維持に関する機器またはシステムに使用することを承認しまたは保証するものではありません。

### 仕樣: 単一電源

特に記述のない限り、 $T_A = -40$  ~+85 、 $V_{CC} = +15$ V、 $V_{DD} = +5$ V、 $V_{SS} = GND$ 、 $V_{REFH} = +10$ V、 $V_{REFL} = 0$ Vです。

|                                                                                                                             |                                                                                                                                           | DAC7724N, U<br>DAC7725N, U                    |                      |                                                        |       | C7724NB,<br>C7725NB, |                                     |                                                                |

|-----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|----------------------|--------------------------------------------------------|-------|----------------------|-------------------------------------|----------------------------------------------------------------|

| パラメータ                                                                                                                       | 条件                                                                                                                                        | 最小                                            | 標準                   | 最大                                                     | 最小    | 標準                   | 最大                                  | 単位                                                             |

| 精度<br>直線性誤差(*)<br>直線性マッチング(*3)<br>微分直線性誤差<br>単調性<br>ゼロスケール誤差<br>ゼロスケール・ドリフト<br>ゼロスケール・マッチング(*3)<br>フルスケール・マッチング(*3)<br>電源感度 | T <sub>MIN</sub> ~T <sub>MAX</sub><br>コード = 004 <sub>H</sub><br>コード = FFF <sub>H</sub><br>フルスケール時                                         | 12                                            | 2 20                 | ±2<br>±2<br>±1<br>±4<br>±4<br>±4<br>±4                 | *     | *                    | ±1<br>±1<br>±1<br>*<br>*<br>±2<br>* | LSB <sup>(2)</sup> LSB LSB Bits LSB ppm/ LSB LSB LSB LSB ppm/V |

| アナログ出力<br>電圧出力 <sup>(4)</sup><br>出力電流<br>負荷キャパシタンス<br>短絡電流<br>短絡時間                                                          | 発振なし<br>対V <sub>cc</sub> またはGND                                                                                                           | V <sub>REFL</sub> ±5                          | 500<br>±20<br>無制限    | $V_{REFH}$                                             | *     | * * *                | *                                   | V<br>mA<br>pF<br>mA                                            |

| <b>リファレンス入力</b><br>V <sub>REFI</sub> 入カレンジ<br>V <sub>REFI</sub> 入カレンジ<br>Ref "ハイ" 入力電流<br>Ref "ロー" 入力電流                     |                                                                                                                                           | V <sub>REFL</sub> + 1.25<br>0<br>-0.3<br>-2.0 |                      | +10<br>V <sub>REFH</sub> - 1.25<br>1.5<br>0            | * * * |                      | * * *                               | V<br>V<br>mA<br>mA                                             |

| <b>ダイナミック性能</b><br>セトリングタイム <sup>(5)</sup><br>チャンネル間クロストーク<br>デジタル・フィードスルー<br>出力雑音電圧                                        | ±0.012%まで、10V出力ステップ<br>f = 10kHz                                                                                                          |                                               | 8<br>0.25<br>2<br>65 | 10                                                     |       | * *                  | *                                   | μs<br>LSB<br>nV-s<br>nV/√Hz                                    |

| デジタル入出力<br>ロジック・ファミリ<br>ロジック・レベル<br>V <sub>H</sub><br>V <sub>C</sub><br>V <sub>OH</sub><br>V <sub>OL</sub><br>データ・フォーマット    | $\begin{split} I_{_{ H}} &\leq \pm 10 \mu A \\ I_{_{ L}} &\leq \pm 10 \mu A \\ I_{_{OH}} &= -0.8 m A \\ I_{_{OL}} &= 1.6 m A \end{split}$ | 2.4<br>-0.3<br>3.6<br>0.0                     | コンパチブル               | V <sub>DD</sub> + 0.3<br>0.8<br>V <sub>DD</sub><br>0.4 | * * * |                      | * * *                               | V<br>V<br>V                                                    |

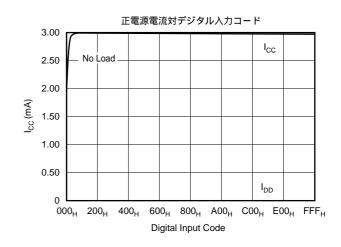

| <b>電源条件</b> V <sub>DD</sub> V <sub>CC</sub> I <sub>DD</sub> I <sub>CC</sub> 消費電力                                            |                                                                                                                                           | +4.75<br>14.25                                | 50<br>3.0<br>45      | +5.25<br>15.75                                         | *     | * *                  | *<br>*<br>*                         | V<br>V<br>μA<br>mA<br>mW                                       |

| <b>温度範囲</b><br>仕様に規定された性能                                                                                                   |                                                                                                                                           | -40                                           |                      | +85                                                    | *     |                      | *                                   |                                                                |

注:(1)  $V_{SS}$  = 0Vの場合、仕様は004 $_{

m H}$ 以上のコードに適用されます。(2) LSBは最下位ビットを意味します。 $V_{REFH}$  = +10V、 $V_{REFH}$  = 0Vの場合、1LSBは2.44mVです。(3) すべてのDAC出力は、仕様に規定された誤差の範囲内でマッチします。(4) ゼロスケール誤差およびフルスケール誤差を含まない理想的な出力電圧です。(5) 正の10Vフルスケール・ステップ、およびコードFFF $_{

m H}$ から004 $_{

m H}$ までの負のステップです。

### 絶対最大定格(1)

| V <sub>cc</sub> ~ V <sub>ss</sub>                  | -0.3V ~ +32V               |

|----------------------------------------------------|----------------------------|

| V <sub>cc</sub> ~ GND                              | 0.3V ~ +16V                |

| V <sub>ss</sub> ~GND                               |                            |

| V <sub>DD</sub> ~ GND                              |                            |

| V <sub>REF</sub> H ~ GND                           | –9V ~ +11V                 |

| V <sub>PEE</sub> L ~ GND( V <sub>SS</sub> = -15V ) | –11V ~ +9V                 |

| $V_{REF}^{NCI}L \sim GND(V_{SS}^{SS} = 0V)$        | 0.3V ~ +9V                 |

| V <sub>REFH</sub> ~ V <sub>REFL</sub>              | 1V ~ +22V                  |

| デジタル入力電圧( 対GND )                                   | $-0.3V \sim V_{DD} + 0.3V$ |

| デジタル出力電圧(対GND)                                     | $-0.3V \sim V_{DD} + 0.3V$ |

| 最大接合部温度                                            | +150                       |

| 動作温度範囲                                             | 40 ~ +85                   |

| 保存温度範囲                                             | 65 ~ +150                  |

| リード温度( 10秒間の半田付け )                                 | +300                       |

注:(1) 定格を超えるオーバ・ストレスは、デバイスに永久的な損傷を与えます。絶対最大条件下に長時間置いた場合は、デバイスの信頼性が低下することがあります。

## 静電気放電対策

この集積回路は静電気によって損傷を受ける場合があります。 すべての集積回路の取り扱いには十分な注意を払ってください。 適切な取り扱いや正しい設置手順の実行を怠った場合、損傷を与 えるおそれがあります。

静電気放電はわずかな性能の低下から完全なデバイスの故障に 至るまで、様々な損傷を与えます。高精度の集積回路は、損傷に 対して敏感であり、極めてわずかなパラメータの変化により、デ バイスに規定された仕様に適合しなくなる場合があります。

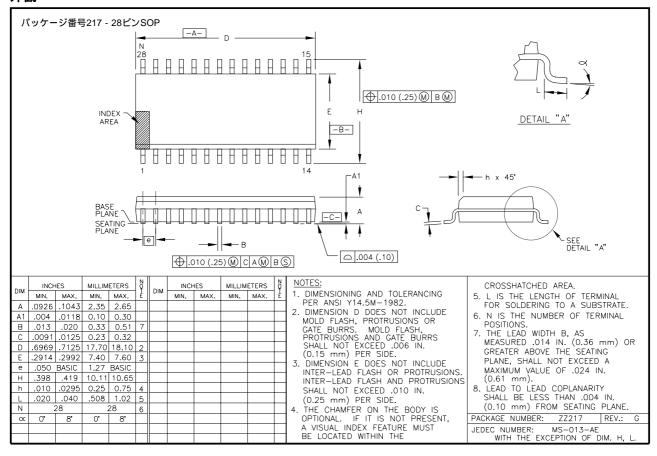

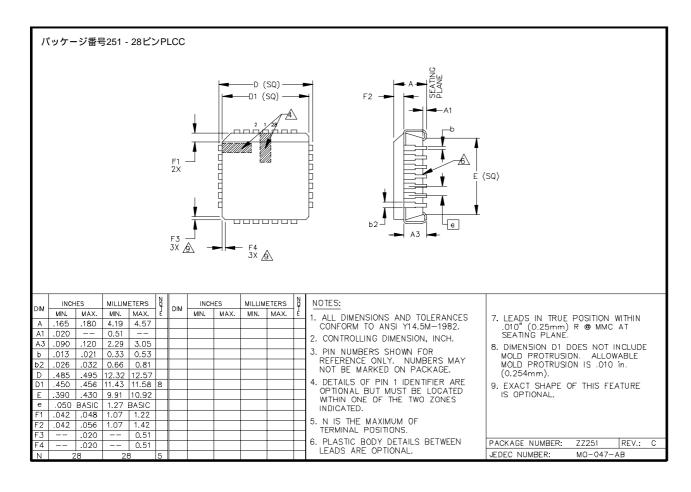

### パッケージ情報/ご発注の手引き

| モデル       | 最大直線性誤差<br>(LSB) | 最大微分非直線性<br>誤差(LSB) | パッケージ    | パッケージ図番号 | 仕様温度範囲                  | <b>発注番号</b> (1) | 供給時の状態 |

|-----------|------------------|---------------------|----------|----------|-------------------------|-----------------|--------|

| DAC7724N  | ±2               | ±1                  | 28ピンPLCC | 251      | -40 ~ <b>+</b> 85       | DAC7724N        | マガジン   |

| DAC7724N  | ±2               | ±1                  | 28ピンPLCC | 251      | <b>−40</b> ~ <b>+85</b> | DAC7724N/750    | テープリール |

| DAC7724NB | ±1               | ±1                  | 28ピンPLCC | 251      | <b>−40</b> ~ <b>+85</b> | DAC7724NB       | マガジン   |

| DAC7724NB | ±1               | ±1                  | 28ピンPLCC | 251      | <b>−40</b> ~ <b>+85</b> | DAC7724NB/750   | テープリール |

| DAC7724U  | ±2               | ±1                  | 28ピンSOP  | 217      | <b>−40</b> ~ <b>+85</b> | DAC7724U        | マガジン   |

| DAC7724U  | ±2               | ±1                  | 28ピンSOP  | 217      | <b>−40</b> ~ <b>+85</b> | DAC7724U/1K     | テープリール |

| DAC7724UB | ±1               | ±1                  | 28ピンSOP  | 217      | <b>−40</b> ~ <b>+85</b> | DAC7724UB       | マガジン   |

| DAC7724UB | ±1               | ±1                  | 28ピンSOP  | 217      | <b>−40</b> ~ <b>+85</b> | DAC7724UB/1K    | テープリール |

| DAC7725N  | ±2               | ±1                  | 28ピンPLCC | 251      | <b>−40</b> ~ <b>+85</b> | DAC7725N        | マガジン   |

| DAC7725N  | ±2               | ±1                  | 28ピンPLCC | 251      | <b>−40</b> ~ <b>+85</b> | DAC7725N/750    | テープリール |

| DAC7725NB | ±1               | ±1                  | 28ピンPLCC | 251      | <b>−40</b> ~ <b>+85</b> | DAC7725NB       | マガジン   |

| DAC7725NB | ±1               | ±1                  | 28ピンPLCC | 251      | <b>−40</b> ~ <b>+85</b> | DAC7725NB/750   | テープリール |

| DAC7725U  | ±2               | ±1                  | 28ピンSOP  | 217      | <b>−40</b> ~ <b>+85</b> | DAC7725U        | マガジン   |

| DAC7725U  | ±2               | ±1                  | 28ピンSOP  | 217      | <b>−40</b> ~ <b>+85</b> | DAC7725U/1K     | テープリール |

| DAC7725UB | ±1               | ±1                  | 28ピンSOP  | 217      | <b>−40</b> ~ <b>+85</b> | DAC7725UB       | マガジン   |

| DAC7725UB | ±1               | ±1                  | 28ピンSOP  | 217      | <b>−40</b> ~ <b>+85</b> | DAC7725UB/1K    | テープリール |

注:(1)スラッシュ(/)が付記されたモデルは、表示数量のテープリールでのみ供給されます(例えば、/750はリール1本あたり750個入りであることを示します)。「DAC7724/750」を発注すると、750個入りテープリールが1本納品されます。

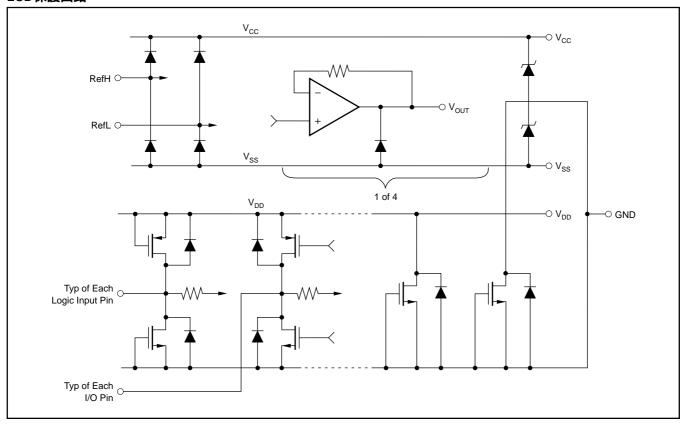

### ESD保護回路

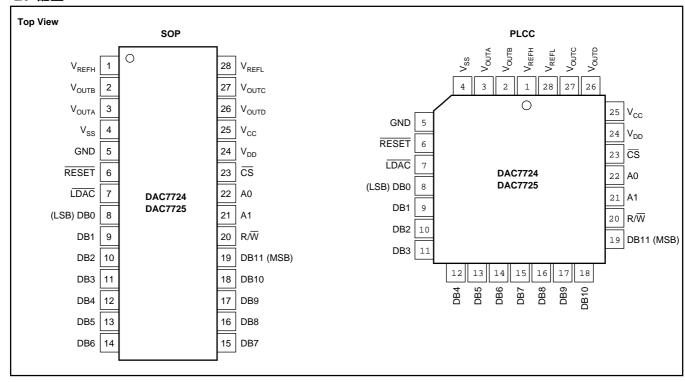

### ピン配置

### ピン構成

| こノ情 | 1176                        |                                                                                                                     |

|-----|-----------------------------|---------------------------------------------------------------------------------------------------------------------|

| ピン  | 名称                          | 説明                                                                                                                  |

| 1   | $V_{REFH}$                  | リファレンス入力電圧" ハイ "、すべてのDACの最大出力電圧を設定。                                                                                 |

| 2   | $V_{OUTB}$                  | DAC B電圧出力                                                                                                           |

| 3   | $V_{OUTA}$                  | DAC A電圧出力                                                                                                           |

| 4   | $V_{ss}$                    | 負のアナログ電源電圧、0Vまたは-15V。                                                                                               |

| 5   | GND                         | グランド                                                                                                                |

| 6   | RESET                       | 非同期リセット入力。" ロー " のとき、DACおよび入力レジスタがミッドスケール( 800 <sub>μ</sub> 、DAC7724 )またはゼロスケール( 000 <sub>μ</sub> 、DAC7725 )に設定される。 |

| 7   | LDAC                        | 負荷DAC入力。"ロー"のとき、すべてのDACレジスタが透過的になる。                                                                                 |

| 8   | DB0                         | データ・ビット0、12ビット・ワードの最下位ビット。                                                                                          |

| 9   | DB1                         | データ・ビット1                                                                                                            |

| 10  | DB2                         | データ・ビット2                                                                                                            |

| 11  | DB3                         | データ・ビット3                                                                                                            |

| 12  | DB4                         | データ・ビット4                                                                                                            |

| 13  | DB5                         | データ・ビット5                                                                                                            |

| 14  | DB6                         | データ・ビット6                                                                                                            |

| 15  | DB7                         | データ・ビット7                                                                                                            |

| 16  | DB8                         | データ・ビット8                                                                                                            |

| 17  | DB9                         | データ・ビット9                                                                                                            |

| 18  | DB10                        | データ・ビット10                                                                                                           |

| 19  | DB11                        | データ・ビット11、12ビット・ワードの最上位ビット。                                                                                         |

| 20  | R/W                         | 読み取り/書き込み制御入力( 読み取り = " 八イ "、書き込み = " ロー ")                                                                         |

| 21  | A1                          | レジスタ/DAC選択 CまたはD = " ハイ "、AまたはB = " ロー ")                                                                           |

| 22  | A0                          | レジスタ/DAC選択(BまたはD = " ハイ "、AまたはC = " ロー ")                                                                           |

| 23  | <u>cs</u>                   | チップ・セレクト入力                                                                                                          |

| 24  | $V_{\scriptscriptstyle DD}$ | 正のデジタル電源、+5V。                                                                                                       |

| 25  | V <sub>cc</sub>             | 正のアナログ電源電圧、公称+15V。                                                                                                  |

| 26  | $V_{\text{OUTD}}$           | DAC D電圧出力                                                                                                           |

| 27  | V <sub>outc</sub>           | DAC C電圧出力                                                                                                           |

| 28  | $V_{REFL}$                  | リファレンス入力電圧"ロー"、すべてのDACの最小出力電圧を設定。                                                                                   |

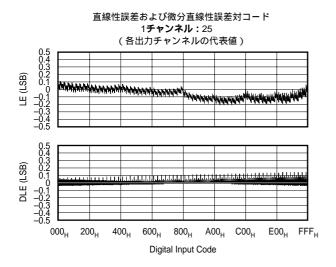

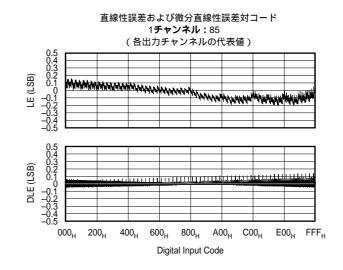

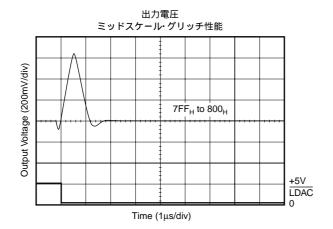

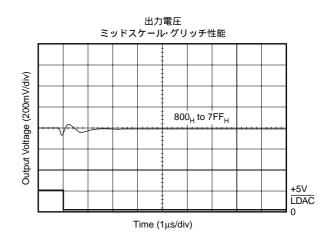

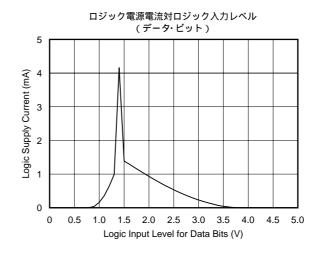

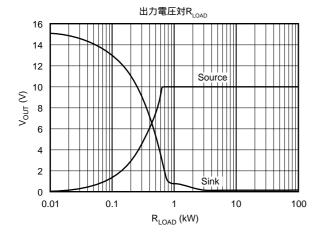

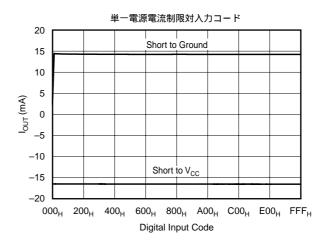

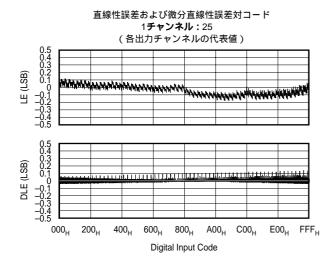

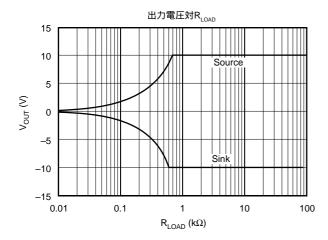

## **代表的性能曲線:**V<sub>SS</sub> = 0V

特に記述のない限り、 $T_{_A}$  = +25 、 $V_{_{CC}}$  = +15V、 $V_{_{DD}}$  = +5V、 $V_{_{SS}}$  = 0V、 $V_{_{REFH}}$  = +10V、 $V_{_{REFL}}$  = 0V、代表的ユニットです。

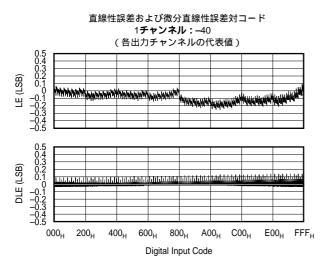

## **代表的性能曲線:**V<sub>SS</sub> = 0V

特に記述のない限り、 $T_A$  = +25 、 $V_{CC}$  = +15V、 $V_{DD}$  = +5V、 $V_{SS}$  = 0V、 $V_{REFH}$  = +10V、 $V_{REFL}$  = 0V、代表的ユニットです。

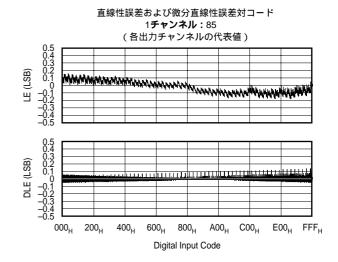

## **代表的性能曲線:**V<sub>SS</sub> = 0V

特に記述のない限り、 $T_{A}$  = +25 、 $V_{CC}$  = +15V、 $V_{DD}$  = +5V、 $V_{SS}$  = 0V、 $V_{REFH}$  = +10V、 $V_{REFL}$  = 0V、代表的ユニットです。

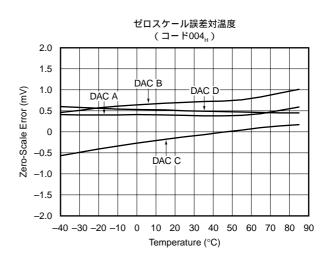

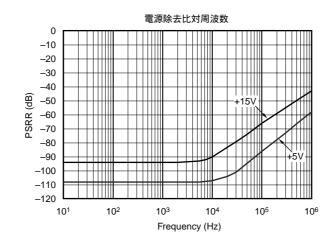

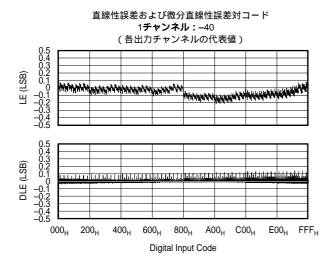

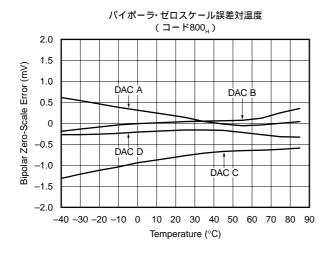

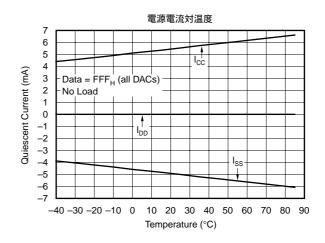

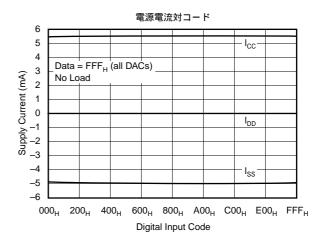

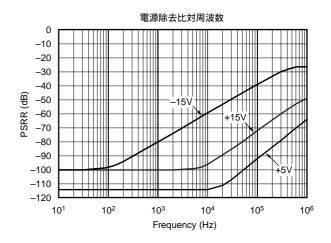

## **代表的性能曲線:**V<sub>SS</sub> = -15V

特に記述のない限り、 $T_A$  = +25 、 $V_{CC}$  = +15V、 $V_{DD}$  = +5V、 $V_{SS}$  = -15V、 $V_{REFH}$  = +10V、 $V_{REFH}$  = -10V、代表的ユニットです。

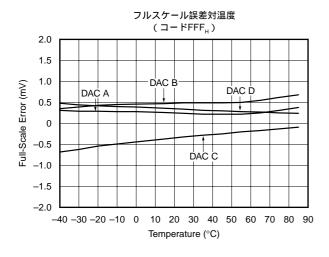

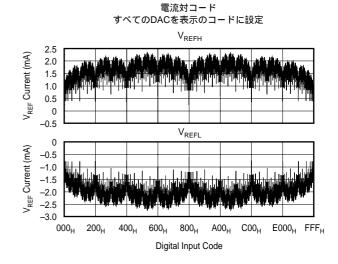

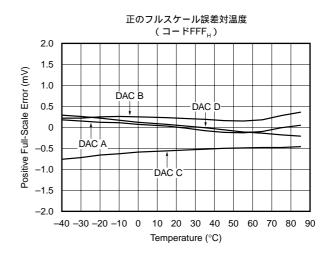

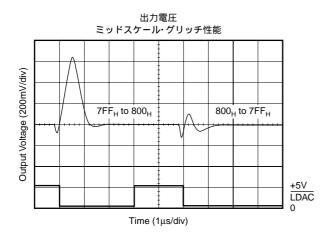

## **代表的性能曲線:**V<sub>SS</sub> = -15V

特に記述のない限り、 $T_{_A}$  = +25 、 $V_{_{CC}}$  = +15V、 $V_{_{DD}}$  = +5V、 $V_{_{SS}}$  = -15V、 $V_{_{REFH}}$  = +10V、 $V_{_{REFH}}$  = -10V、代表的ユニットです。

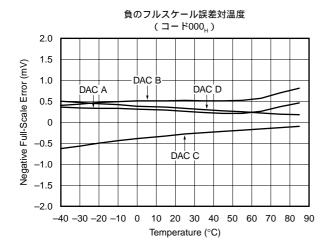

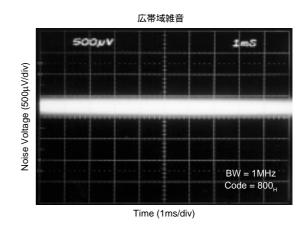

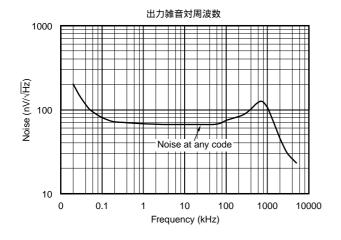

# **代表的性能曲線:**V<sub>ss</sub> = -15V

特に記述のない限り、 $T_{_A}$  = +25 、 $V_{_{CC}}$  = +15V、 $V_{_{DD}}$  = +5V、 $V_{_{SS}}$  = -15V、 $V_{_{REFH}}$  = +10V、 $V_{_{REFH}}$  = -10V、代表的ユニットです。

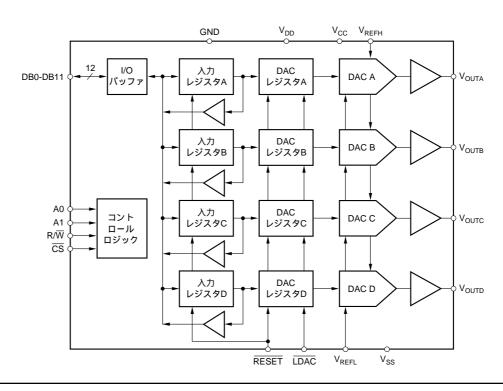

### 動作原理

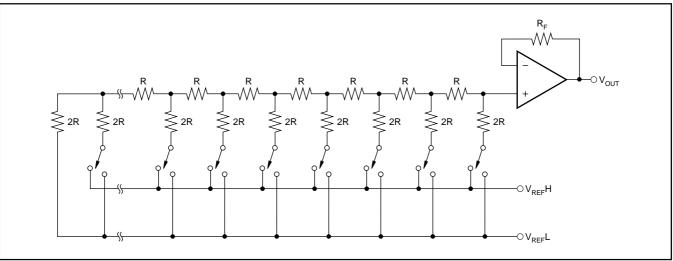

DAC7724およびDAC7725は、12ビット、クワッド・タイプの電圧出力D/Aコンバータ(DAC)です。アーキテクチャは、図1に示すように、クラシックなR-2Rラダー構成で、後段にバッファとして機能するオペアンプがあります。各DACごとにR-2Rラダー・ネットワークと出力オペアンプがありますが、リファレンス電圧入力はすべてのDACで共有しています。最小電圧出力(ゼロスケール)および最大電圧出力(フルスケール)は、それぞれ外部電

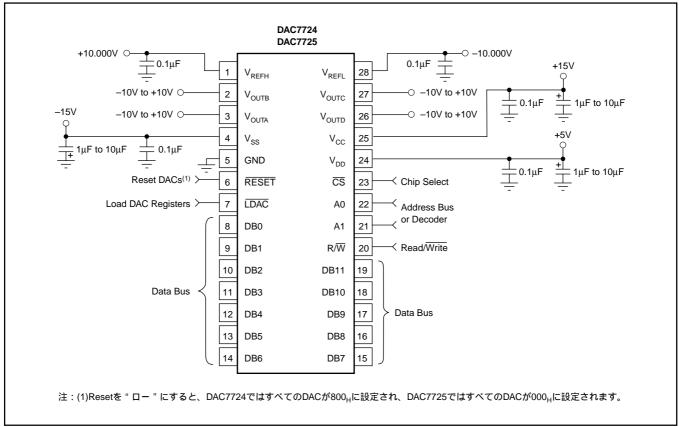

圧リファレンスV<sub>REFL</sub>およびV<sub>REFH</sub>によって設定します。デジタル入力は12ビットのパラレル・ワードであり、DAC入力レジスタにはリードバック機能があります。このコンバータは、+15Vの単一電源または±15Vのデュアル電源で動作させることができます。各デバイスはリセット機能を備えており、すべてのDACレジスタおよびDAC出力電圧を直ちにミッドスケール(DAC7724、800<sub>H</sub>)またはゼロスケール(DAC7725、000<sub>H</sub>)に設定します。DAC7724/25の基本動作については、図2および図3を参照してください。

図1. DAC7724/25のアーキテクチャ

図2. DAC7724/25**の基本的な単一電源動作**

図3. DAC7724/25の基本的なデュアル電源動作

### アナログ出力

$V_{ss}=-15$ V(デュアル電源動作)のとき、出力アンプは電源レールの4V以内までスイングでき、-40 ~+85 の温度範囲にわたり保証されています。 $V_{ss}=0$ V(単一電源動作)で $R_{LOAD}$ をグランドに接続したとき、出力はグランドまでスイングできます。グランドにきわめて近い電圧では、出力オペアンプのセトリングタイムが長くなることに注意してください。 $V_{ss}=0$ Vのときは、ゼロスケール誤差の測定にも注意が必要です。出力アンプに負のオフセットがある場合、出力電圧はグランド以下にスイングできないため、最初のいくつかのデジタル入力コード( $000_{H}$ 、 $001_{H}$ 、 $002_{H}$  など)に対して出力電圧が変化しないことがあります。単一電源の場合、負のオフセットの制限値が-4LSB(-9.76mV)で、仕様が規定される最初の出力はコード $004_{H}$ となります。

#### リファレンス入力

デュアル電源動作の場合、リファレンス入力 $V_{REFL}$ および $V_{REFH}$ は、 $V_{REFH}$ が $V_{REFL}$ より1.25V以上高い限り、 $V_{SS}$  + 4Vから $V_{CC}$  - 4Vまでの任意の電圧を使用することができます。単一電源動作( $V_{SS}$  = 0V)の場合、同様に $V_{REFH}$ が $V_{REFL}$ より1.25V以上高い限り、 $V_{REFL}$ は0V以上の任意の電圧を使用できます。各DACの最小出力は、 $V_{REFL}$ にわずかなオフセット電圧(ほぼ出力オペアンプのオフセット)を加えたものになります。最大出力は、 $V_{REFH}$ に同様のオフセット電圧を加えたものになります。 $V_{SS}$  負電源  $V_{SS}$  は、グランドに接続するか、 $V_{SS}$  の電圧によって、コンバータ内部の複数のバイアス・ポイントが設定されます。 $V_{SS}$  がこれらの値になっていない場合、バイアス値が不正になり、デバイスの正しい動作が保証されません。

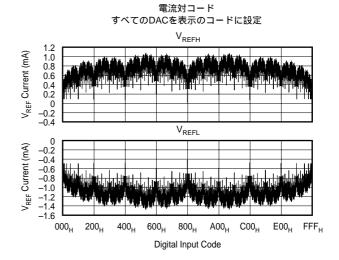

V<sub>REFH</sub>入力に流れ込む電流およびV<sub>REFL</sub>から流れ出す電流は、DACの出力電圧に依存し、数μAから約0.3mAまでの範囲で変動します。リファレンス入力は、リファレンスに対する可変負荷として作用します。リファレンスで必要なシンク電流またはソース電流が得られるならば、リファレンス・パッファは必要ありません。代表的性能曲線の「リファレンス電流対コード」を参照してください。

アナログ電源は、リファレンス電源と同時か、それより先にオンになる必要があります。リファレンスの電源が先にオンになると、V<sub>cc</sub>とV<sub>ss</sub>の電源は「ESD保護ダイオードを介してリファレンスから電源が供給される」状態になります(ESD保護回路を参照)。DAC7724/25パッケージのできるだけ近くに0.1μF以上のコンデンサを配置してリファレンス電圧をバイパスすることを強く推奨します。

#### デジタル・インターフェース

表Iに、DAC7724/25の基本的な制御ロジックを示します。各内部レジスタはレベル・トリガであり、エッジ・トリガではないことに注意してください。対応する信号がローでなると、レジスタは透過的になります。この信号がハイで戻ると、現在レジスタ内にあるデジタル・ワードがラッチされます。最初のレジスタ・セット(入力レジスタ)は、AO、A1、R/W、およびCS入力によってトリガされます。これらのレジスタのうち、同時に透過的になるのは1つだけです。2番目のレジスタ・セット(DACレジスタ)は、LDAC入力がローでなるとすべて透過的になります。

各DACは、対応する入力レジスタに書き込んでからDACレジスタを更新することにより、それぞれ独立して更新できます。ま

たは、LDACを ロー に維持することで、DACレジスタ全体が常に透過的になるように設定することもできます。DACの更新は、 入力レジスタに書き込まれたときに行われます。

ダブル・バッファリング・アーキテクチャの主な目的は、各DAC入力レジスタにいつでも書き込むことができ、その後でLDACを ロー "にしてすべてのDAC出力電圧を同時に更新できるようにすることです。また、DAC入力レジスタに任意の時点で書き込んで、LDACに接続されたトリガ信号を介してDAC電圧を同時に変更することもできます。

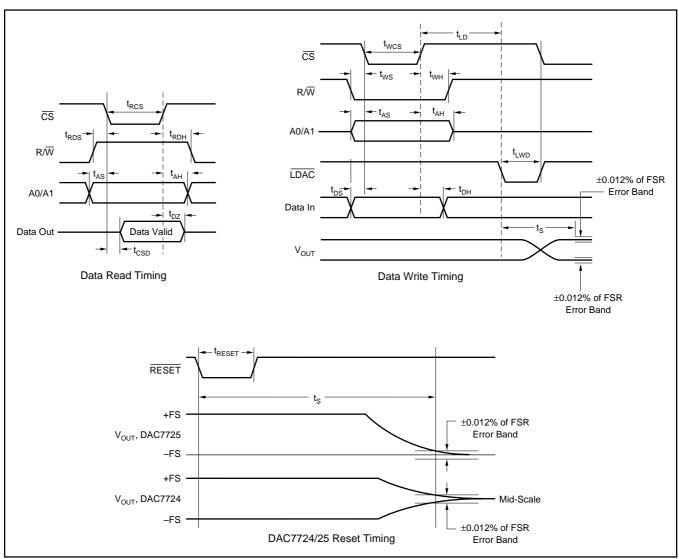

### デジタル・タイミング

図4と表IIに、DAC7724およびDAC7725のデジタル・インターフェースの詳細なタイミングを示しています。

### デジタル入力コーディング

DAC7724**および**DAC7725**の入力データは、ストレート・バイナ** リ・フォーマットです。出力電圧は次の式で与えられます。

$$V_{OUT} = V_{REFL} + \frac{(V_{REFH} - V_{REFL}) \cdot N}{4096}$$

ここでNはデジタル入力コードです。この式には、オフセット (ゼロスケール)誤差の影響は含まれていません。

| A1   | A0 | R/W | <del>CS</del> | RESET            | LDAC | 選択される<br>入力レジスタ | 選択された<br>入力レジスタの状態 | <b>すべての</b><br>DAC <b>レジスタの状態</b> |

|------|----|-----|---------------|------------------|------|-----------------|--------------------|-----------------------------------|

| L(1) | L  | L   | L             | H <sup>(2)</sup> | L    | А               | 透過的                | 透過的                               |

| L    | Н  | L   | L             | Н                | L    | В               | 透過的                | 透過的                               |

| Н    | L  | L   | L             | Н                | L    | С               | 透過的                | 透過的                               |

| Н    | Н  | L   | L             | Н                | L    | D               | 透過的                | 透過的                               |

| L    | L  | L   | L             | Н                | Н    | А               | 透過的                | ラッチ                               |

| L    | Н  | L   | L             | Н                | Н    | В               | 透過的                | ラッチ                               |

| Н    | L  | L   | L             | Н                | Н    | С               | 透過的                | ラッチ                               |

| Н    | Н  | L   | L             | Н                | Н    | D               | 透過的                | ラッチ                               |

| L    | L  | Н   | L             | Н                | Н    | Α               | リードバック             | ラッチ                               |

| L    | Н  | Н   | L             | Н                | Н    | В               | リードバック             | ラッチ                               |

| Н    | L  | Н   | L             | Н                | Н    | С               | リードバック             | ラッチ                               |

| Н    | Н  | Н   | L             | Н                | Н    | D               | リードバック             | ラッチ                               |

| X(3) | Х  | Х   | Н             | Н                | L    | なし              | (すべてラッチ)           | 透過的                               |

| X    | X  | Х   | Н             | Н                | Н    | なし              | (すべてラッチ)           | ラッチ                               |

| Х    | Х  | Х   | Х             | L                | Х    | すべて             | リセット(4)            | リセット(4)                           |

注:(1  $\upmu$  = ロジッグ ロー "。(2  $\upmu$  = ロジッグ ハイ "。(3  $\upmu$  = 無視 4  $\upmu$  A  $\upmu$  A  $\upmu$  にリセットされます。 DAC7725は000 $\upmu$  にリセットされます。 RESET が立ち上がると、ラッチされた状態のレジスタはすべてリセット値を保持します。

表I. DAC7724とDAC7725の制御ロジック真理値表

図4. デジタル入力および出力のタイミング

| 記号                 | 説明                                 | 最小  | 標準  | 最大  | 単位 |

|--------------------|------------------------------------|-----|-----|-----|----|

| t <sub>RCS</sub>   | 読み取り時の <del>CS</del> "ロー"          | 200 |     |     | ns |

| t <sub>RDS</sub>   | R/Ѿ" ハイ "から <del>CS</del> " ロー "まで | 10  |     |     | ns |

| t <sub>RDH</sub>   | ¯S" ハイ "後のR/W" ハイ "                | 10  |     |     | ns |

| t <sub>DZ</sub>    | ◯S" ハイ "からデータ・バスのハイ・インピーダンスまで      |     | 100 |     | ns |

| t <sub>CSD</sub>   | <del>CS</del> " ロー "からデータ・バス有効まで   |     | 100 | 160 | ns |

| t <sub>wcs</sub>   | 書き込み時のCS" ロー "                     | 50  |     |     | ns |

| t <sub>ws</sub>    | R/Ѿ" ロー "から <del>CS</del> " ロー "まで | 0   |     |     | ns |

| t <sub>wH</sub>    | CS" ハイ "後のR/W" ロー "                | 0   |     |     | ns |

| t <sub>AS</sub>    | アドレス有効から <del>CS</del> " ロー "まで    | 0   |     |     | ns |

| t <sub>AH</sub>    | <br>CS" ハイ "後のアドレス有効               | 0   |     |     | ns |

| t <sub>LD</sub>    | CS" ハイ "からのLDAC遅延                  | 10  |     |     | ns |

| t <sub>DS</sub>    | データ有効から <del>CS</del> " ロー "まで     | 0   |     |     | ns |

| t <sub>DH</sub>    | <del>CS</del> " ハイ "後のデータ有効        | 0   |     | 1   | ns |

| t <sub>LWD</sub>   | LDAC" □ – "                        | 50  |     | 1   | ns |

| t <sub>RESET</sub> | RESET" ロー "時間                      | 50  |     | 1   | ns |

| t <sub>s</sub>     | セトリングタイム                           |     |     | 10  | μs |

表II. タイミング仕様(T<sub>A</sub> = -40 ~+85 )

### 外観

16 ©BBJ000702K