# デュアル、500kHz、12ビット、2+2チャンネル 同時サンプリングA/Dコンバータ

# 特長

4入力チャンネル 完全な差動入力

最大スループット: 2µs(1チャンネルあたり)

ノー・ミッシング・コードを保証 パラレル・インターフェース

実効サンプリング・レート: 1MHz

低消費電力: 40mW

## アプリケーション

モータ制御 多軸ポジショニング・システム

3相電源制御

### 概要

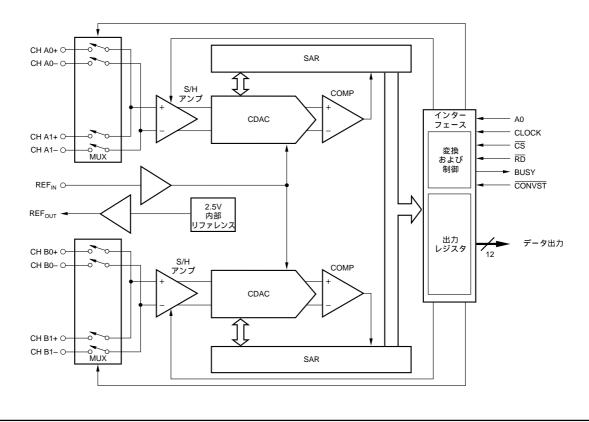

ADS7862は、2組のペアに分けて高速な同時信号アクイジションを実行できる4つの完全な差動入力チャンネルを備えたデュアル・タイプの12ビット、500kHz、A/Dコンバータです。サンプル/ホールド・アンプの入力は完全な差動で、A/Dコンバータの入力まで差動が保たれます。このため、雑音の大きい環境で重要な同相モード除去が50kHzで80dBと優れています。

ADS7862は、ソフトウェアのオーバーヘッドを最小限に抑えるパラレル・インターフェースと制御入力を備えています。各チャンネルのデータは、12ピット・ワードとして出力されます。パッケージは、32ピンTQFPで供給され、すべて-40 ~+85 の動作温度範囲で仕様が規定されています。

PDSJ-1475A December,1998

### 仕樣

特に記述のない限り、 $T_{A} = T_{MIN} \sim T_{MAX}$ 、 $+V_{A} = + V_{D} = +5V$ 、 $V_{REF} = +2.5V$ 内部リファレンス、 $f_{CLK} = 8MHz$ 、 $f_{SAMPLE} = 500kHz$ です。

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                          |                                   | ADS7862Y                                                                    |                                                                     | ADS7862YB |                                         |                               | ]                                                       |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|-----------------------------------------------------------------------------|---------------------------------------------------------------------|-----------|-----------------------------------------|-------------------------------|---------------------------------------------------------|--|

| パラメータ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 条件                                                                                                                                                                                                                       | 最小                                | 標準                                                                          | 最大                                                                  | 最小        | 標準                                      | 最大                            | 単位                                                      |  |

| 分解能                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                          |                                   |                                                                             | 12                                                                  |           |                                         | *                             | Bits                                                    |  |

| アナログ入力         入力電圧範囲、パイポーラ         絶対入力範囲         入力キャパシタンス         入力リーク電流                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | V <sub>CENTER</sub> = 内部V <sub>REF</sub> 2.5V<br>+IN<br>-IN<br>CLK = GND                                                                                                                                                 | -V <sub>REF</sub><br>-0.3<br>-0.3 | 15<br>±1                                                                    | +V <sub>REF</sub><br>V <sub>CC</sub> + 0.3<br>V <sub>CC</sub> + 0.3 | *         | *                                       | *                             | V<br>V<br>V<br>pF<br>μA                                 |  |

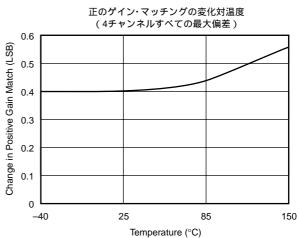

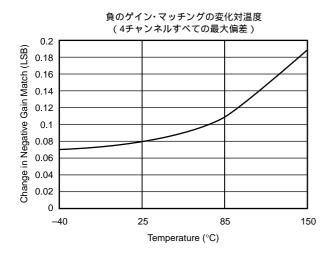

| システム性能 ノー・ミッシング・コード 積分直線性 積分直線性 パイポーラ・オフセット誤差 パイポーラ・オフセット誤差のマッチング 正のゲイン誤差のマッチング 直のゲイン誤差 負のゲイン誤差 自のゲイン誤差 はいません はい | REF <sub>IN</sub> 基準<br>REF <sub>IN</sub> 基準<br>REF <sub>IN</sub> 基準<br>DC<br>V <sub>IN</sub> = ±1.25Vp-p、50kHz                                                                                                          | 12                                | ±0.75<br>0.5<br>±0.75<br>±0.75<br>±0.15<br>±0.15<br>80<br>80<br>120<br>±0.5 | ±2<br>1<br>±3<br>3<br>±0.75<br>2<br>±0.75<br>2                      | •         | ±0.5  ±0.5  ±0.5  ±0.1  ±0.1  *  *  *   | ±1  * ±1 ±2 2 ±0.5 1 ±0.5 1 * | Bits LSB LSB LSB LSB LSB So of FSR LSB GB GB  µVrms LSB |  |

| サンプリング特性<br>変換時間( A/D1個あたり )<br>アクイジション時間<br>スループット・レート<br>アパーチャ遅延<br>アパーチャ遅延のマッチング<br>アパーチャ・ジッタ<br>小信号帯域幅                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                          | 500                               | 1.75<br>0.25<br>3.5<br>100<br>50<br>40                                      |                                                                     | *         | * * * * * *                             |                               | μs<br>μs<br>kHz<br>ns<br>ps<br>ps<br>MHz                |  |

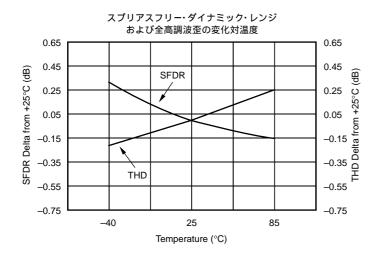

| <b>ダイナミック特性</b><br>全高調波歪<br>SINAD<br>スプリアスフリー・ダイナミック・レンジ<br>チャンネル間の分離                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | $V_{_{IN}} = \pm 2.5 \text{Vp-p}, \ 100 \text{kHz}$<br>$V_{_{IN}} = \pm 2.5 \text{Vp-p}, \ 100 \text{kHz}$<br>$V_{_{IN}} = \pm 2.5 \text{Vp-p}, \ 100 \text{kHz}$<br>$V_{_{IN}} = \pm 2.5 \text{Vp-p}, \ 100 \text{kHz}$ |                                   | 75<br>71<br>–78                                                             | -80                                                                 |           | * *                                     | *                             | dB<br>dB<br>dB<br>dB                                    |  |

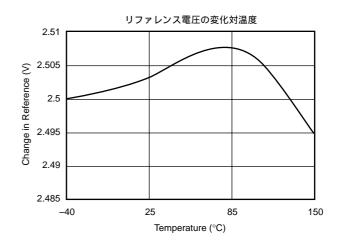

| リファレンス電圧<br>内部<br>内部ドリフト<br>内部雑音<br>内部ソース電流<br>内部負荷除去<br>内部PSRR<br>外部電圧範囲<br>入力電流<br>入力キャパシタンス                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                          | 2.475                             | 2.5<br>±25<br>50<br>2<br>0.005<br>65<br>2.5<br>0.05<br>5                    | 2.525<br>2.6<br>1                                                   |           | * * * * * * * * * * * * * * * * * * * * | *                             | V<br>ppm/<br>µVp-p<br>mA<br>mV/µA<br>dB<br>V<br>µA      |  |

| <b>デジタル入出力</b><br>ロジック・ファミリ<br>ロジック・レベル:V <sub>IH</sub><br>V <sub>IL</sub><br>V <sub>OH</sub><br>外部クロック<br>データ・フォーマット                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | $I_{IH} = +5\mu A$ $I_{IL} = +5\mu A$ $I_{OH} = -500\mu A$ $I_{OL} = 500\mu A$                                                                                                                                           | 3.0<br>-0.3<br>3.5<br>0.2         | CMOS<br>「イナリ2の補                                                             | +V <sub>DD</sub> + 0.3<br>0.8<br>0.4<br>8<br>数                      | * *       | *                                       | * * *                         | V<br>V<br>V<br>WHz                                      |  |

| <b>電源条件</b><br>電源電圧、+V<br>無信号時電流、+V <sub>A</sub><br>消費電力                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                          | 4.75                              | 5<br>5<br>25                                                                | 5.25<br>8<br>40                                                     | *         | * *                                     | * *                           | V<br>mA<br>mW                                           |  |

<sup>\*</sup>印は、ADS7862Yのグレードと同じ値であることを示します。

このデータシートに記載されている情報は、信頼し得るものと考えておりますが、不正確な情報や記載漏れ等に関して弊社は責任を負うものではありません。情報の使用について弊社は責任を負えませんので、各ユーザーの責任において御使用下さい。価格や仕様は予告なしに変更される場合がありますのでご了承下さい。ここに記載されているいかなる回路についても工業所有権その他の権利またはその実施権を付与したり承諾したりするものではありません。弊社は弊社製品を生命維持に関する機器またはシステムに使用することを承認しまたは保証するものではありません。

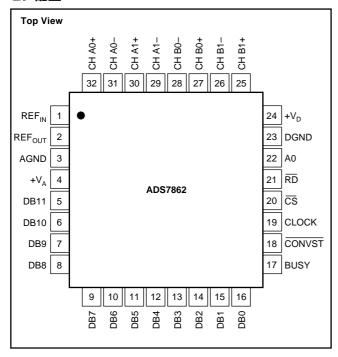

### ピン配置

#### 絶対最大定格

| アナログ入力( 対AGND、任意のチャンネル入力 ). – | $0.3V \sim (+V_D + 0.3V)$ |

|-------------------------------|---------------------------|

| REF <sub>IN</sub>             | $0.3V \sim (+V_D + 0.3V)$ |

| デジタル入力( 対DGND )               |                           |

| グランド電圧の差:AGND、DGND            | ±0.3V                     |

| +V <sub>D</sub> ~ AGND        | 0.3V ~ +6V                |

| 消費電力                          | 325mW                     |

| 最大接合部温度                       | +150                      |

| 動作温度範囲                        | 40 ~ +85                  |

| 保存温度範囲                        | 65 ~ +150                 |

| リード温度( 10秒間の半田付け )            | +300                      |

|                               |                           |

# 静電気放電対策

静電気放電はわずかな性能の低下から完全なデバイスの故障に 至るまで、様々な損傷を与えます。すべての集積回路は、適切 なESD保護方法を用いて、取扱いと保存を行うようにして下さ い。高精度の集積回路は、損傷に対して敏感であり、極めてわ ずかなパラメータの変化により、デバイスに規定された仕様に 適合しなくなる場合があります。

### ピン構成

| ピン | 記号                 | 説明                                                                                                                                                  |

|----|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| 1  | REF <sub>IN</sub>  | リファレンス入力                                                                                                                                            |

| 2  | REF <sub>OUT</sub> | +2.5Vリファレンス出力。内部リファレンスを使用する<br>ときはREF <sub>n</sub> ( ピン1 )に直接接続する。                                                                                  |

| 3  | AGND               | アナログ・グランド                                                                                                                                           |

| 4  | +V <sub>A</sub>    | アナログ電源。+5VDC。デジタル電源 ピン24 )に直接接<br>続する。0.1μFのセラミック・コンデンサと10μFのタン<br>タル・コンデンサでアナログ・グランドにデカップリング<br>する。                                                |

| 5  | DB11               | データ・ビット11、MSB                                                                                                                                       |

| 6  | DB10               | データ・ビット10                                                                                                                                           |

| 7  | DB9                | データ・ビット9                                                                                                                                            |

| 8  | DB8                | データ・ビット8                                                                                                                                            |

| 9  | DB7                | データ・ビット7                                                                                                                                            |

| 10 | DB6                | データ・ビット6                                                                                                                                            |

| 11 | DB5                | データ・ビット5                                                                                                                                            |

| 12 | DB4                | データ・ビット4                                                                                                                                            |

| 13 | DB3                | データ・ビット3                                                                                                                                            |

| 14 | DB2                | データ・ビット2                                                                                                                                            |

| 15 | DB1                | データ・ビット1                                                                                                                                            |

| 16 | DB0                | データ・ビット0、LSB                                                                                                                                        |

| 17 | BUSY               | 変換中" ハイ "になる                                                                                                                                        |

| 18 | CONVST             | 变換開始                                                                                                                                                |

| 19 | CLOCK              | CMOSコンパチブルの外部クロックをCLOCK入力に印加することにより変換プロセスを外部ソースと同期させることができる。CLOCKピンは、CLOCK = $16 \cdot f_{SAMPLE}$ の式によりサンブリング・レートを制御する。                            |

| 20 | CS                 | チップ・セレクト                                                                                                                                            |

| 21 | RD                 | パラレル出力の同期パルス。読み取り動作時、最初の立ち下がりエッジでAレジスタが選択され、2番目のエッジでBレジスタが選択される。A0が入力0または入力1の読み取りを制御する。                                                             |

| 22 | A0                 | A0が"ロー"のとき、変換開始の立ち下がりエッジでチャンネルA0とチャンネルB0が変換され、A0が"ハイ"のときチャンネルB1が変換される。読み取り動作時、RDの最初の立ち下がりエッジでAレジスタが選択され、2番目のエッジでBレジスタが選択される。A0が入力0または入力1の読み取りを制御する。 |

| 23 | DGND               | デジタル・グランド。アナログ・グランド(ピン3)に直接<br>接続する。                                                                                                                |

| 24 | +V <sub>D</sub>    | デジタル電源、+5VDC                                                                                                                                        |

| 25 | CH B1+             | 非反転入力チャンネルB1                                                                                                                                        |

| 26 | CH B1-             | 反転入力チャンネルB1                                                                                                                                         |

| 27 | CH B0+             | 非反転入力チャンネルB0                                                                                                                                        |

| 28 | CH B0-             | 反転入力チャンネルB0                                                                                                                                         |

| 29 | CH A1-             | 反転入力チャンネルA1                                                                                                                                         |

| 30 | CH A1+             | 非反転入力チャンネルA1                                                                                                                                        |

| 31 | CH A0-             | 反転入力チャンネルA0                                                                                                                                         |

| 32 | CH A0+             | 非反転入力チャンネルA0                                                                                                                                        |

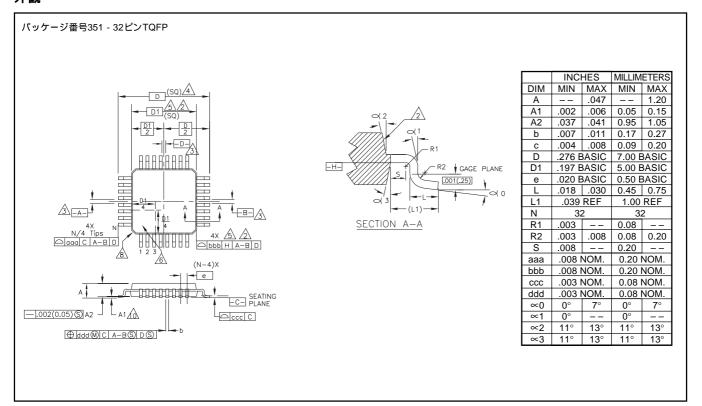

### パッケージ情報/ご発注の手引き

| モデル       | 最小相対精度<br>(LSB) | 最大ゲイン誤差<br>(%) | 仕樣温度範囲                  | パッケージ    | パッケージ<br>図番号(1) | <b>発注番号</b> (2) | 供給時の状態 |

|-----------|-----------------|----------------|-------------------------|----------|-----------------|-----------------|--------|

| ADS7862Y  | ±2              | ±0.75          | -40 ~ <b>+</b> 85       | 32ピンTQFP | 351             | ADS7862Y/250    | テープリール |

| ADS7862Y  | ±2              | ±0.75          | <b>−40</b> ~ <b>+85</b> | 32ピンTQFP | 351             | ADS7862Y/2K     | テープリール |

| ADS7862YB | ±1              | ±0.5           | <b>−40</b> ~ <b>+85</b> | 32ピンTQFP | 351             | ADS7862YB/250   | テープリール |

| ADS7862YB | ±1              | ±0.5           | <b>−40</b> ~ <b>+85</b> | 32ピンTQFP | 351             | ADS7862YB/2K    | テープリール |

注:(1)詳細図および寸法表は、データシートの巻末を参照して下さい。(2)スラッシュ(/)が付記されたモデルは、表示数量のテープリールでのみ供給されます(例えば、/2Kはリール1本あたり2,000個入りのデバイスであることを示します)。"ADS7862Y/2K"を発注すると、2,000個入りテープリール1本が納品されます。

### 基本動作

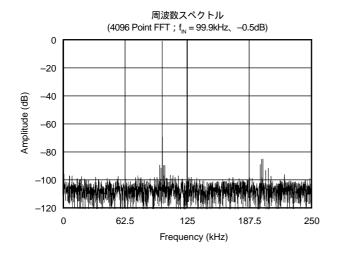

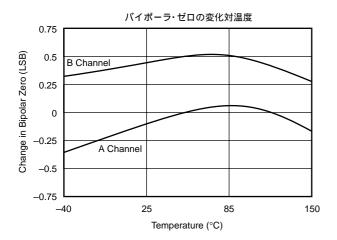

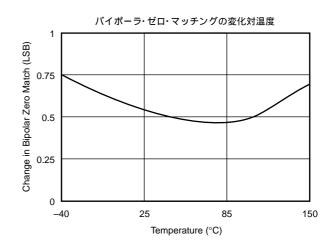

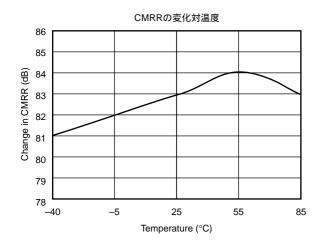

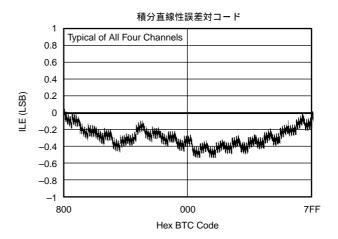

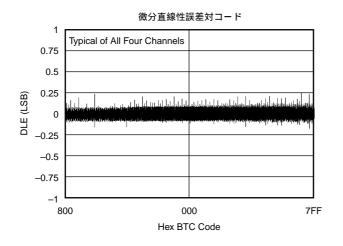

# 代表的性能曲線

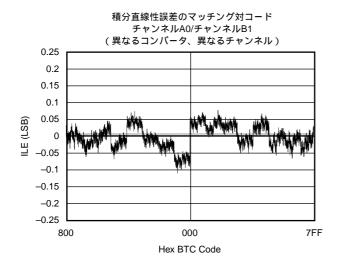

特に記述のない限り、 $T_A$  = +25 、  $+V_A$  =  $+V_D$  = +5V、 $V_{REF}$  = +2.5V内部リファレンス、 $f_{CLK}$  = 8MHz、 $f_{SAMPLE}$  = 500kHzです。

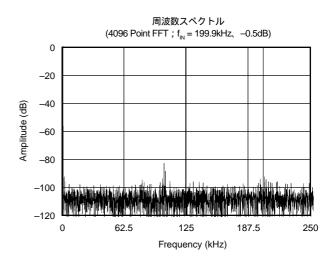

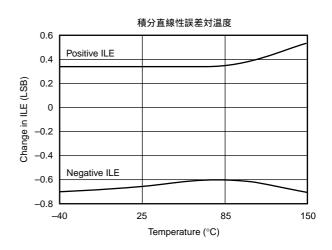

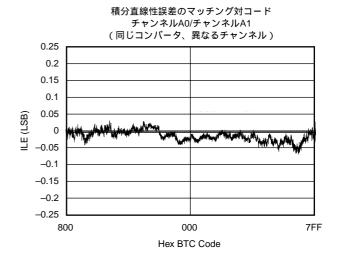

# 代表的性能曲線

特に記述のない限り、 $T_A$  = +25 、  $+V_A$  =  $+V_D$  = +5V、 $V_{REF}$  = +2.5V内部リファレンス、 $f_{CLK}$  = 8MHz、 $f_{SAMPLE}$  = 500kHzです。

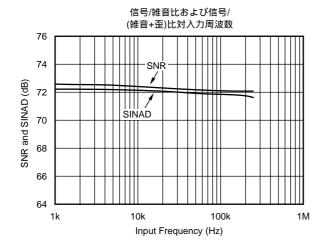

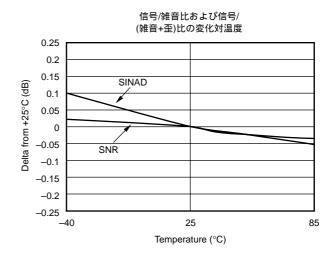

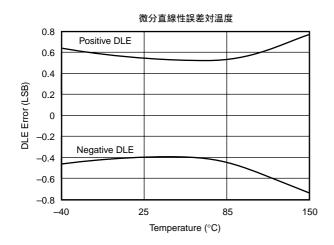

# 代表的性能曲線

特に記述のない限り、 $T_A$  = +25 、  $+V_A$  =  $+V_D$  = +5V、 $V_{REF}$  = +2.5V内部リファレンス、 $f_{CLK}$  = 8MHz、 $f_{SAMPLE}$  = 500kHzです。

### はじめに

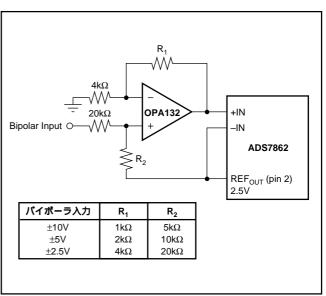

ADS7862は、+5V単一電源で動作する高速で低消費電力なデュ アル・タイプの12ビットA/Dコンバータです。入力チャンネルは 完全な差動で、同相モード除去の標準値は80dBです。ADS7862 は、デュアル2us逐次比較型ADC、2つの差動サンプル/ホール ド・アンプ、+2.5V内部リファレンスとREF」、およびREFOUT ン、高速なパラレル・インターフェースを内蔵しています。2組 のチャンネル(AとB) に分かれた4つのアナログ入力があり、A0入 力でチャンネルを選択します(A0が " ロー " のときチャンネルA0 とB0、A0が"ハイ"のときチャンネルA1とB1が選択されま す)。各A/Dコンパータの2つの入力(A0とA1、B0とB1)を同時に サンプリングして変換できるため、両方のアナログ入力の信号 の相対的な位相情報が保存されます。アナログ入力には、+2.5V 内部リファレンスを中心とする-VRFFから+VRFFまでの電圧を入力 することができます。フロント・エンドにレベル・シフト回路を 使用して、パイポーラ電圧を入力することもできます(図7を参 照)。

でONVSTピンを15ns以上"ロー"にすることにより、ADS7862の変換が開始されます。でONVSTを"ロー"にすると、両方のサンプル/ホールド・アンプが同時にホールド状態になり、両方のチャンネルで変換プロセスが開始されます。BUSY出力ピンは"ハイ"になり、変換サイクルの間"ハイ"に保持されます。A0ピンのステータスに応じて、チャンネル0(A0が"ロー")またはチャンネル1(A0が"ハイ")の変換結果がデータに反映されます。変換後、RDおよびでSを両方とも"ロー"にすることにより、パラレル出力バスからデータを読み取ることができます。

ADS7862の変換時間は、8MHzの外部クロックを使用したとき 1.75μsになります。対応するアクイジション時間は0.25μsです。 次の変換の開始時に直ちに読み取り機能を実行することにより、最大出力レート(500kHz)を達成することができます。

注:この動作モードの詳細については、「タイミングおよび制御」を参照して下さい。

#### サンプル/ホールド部

ADS7862のサンプル/ホールド・アンプにより、ADCはフルスケール振幅の入力正弦波を12ビットの精度まで正確に変換することができます。サンプル/ホールドの入力帯域幅は、ADCが500kHzの最大スループット・レートで動作するときも、ADCのナイキスト・レート(ナイキストはサンプリング・レートの1/2)より高くなります。サンプル/ホールド・アンプの小信号帯域幅の標準値は40MHzです。

標準的なアパーチャ遅延時間、すなわちCONVSTパルスの後にサンプル・モードからホールド・モードへ切り替えるためにADS7862が必要とする時間は、3.5nsです。反復されたアパーチャ遅延の値の平均デルタは、標準値で50psです(アパーチャ・ジッタとも呼びます)。これらの仕様は、AC入力信号を同時に正確にキャプチャするADS7862の能力を反映しています。

#### リファレンス

通常動作では、REF<sub>OUT</sub>ピン(ピン2)をREF<sub>IN</sub>ピン(ピン1)に直接接続してADS7862に+2.5Vの内部リファレンスを供給します。一方、1.2Vから2.6Vまでの外部リファレンスを使用して(対応するフルスケール・レンジは2.4Vから5.2Vまで)ADS7862を動作させることもできます。

ADS7862の内部リファレンスはダブル・バッファリングされます。内部リファレンスを使用して外部負荷をドライブする場合、リファレンスとピン2の負荷の間のバッファが使用されます(内部リファレンスは標準で2mAの電流をソースし、負荷のキャパシタンスが100pFを超えないことが必要です)。外部リファレンスを使用する場合は、2番目のバッファによって外部リファレンスとCDACが分離されます。このバッファは、変換中に両方のCDACのすべてのキャパシタを再充電する目的にも使用されます。

#### アナログ入力

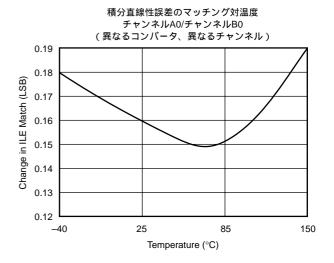

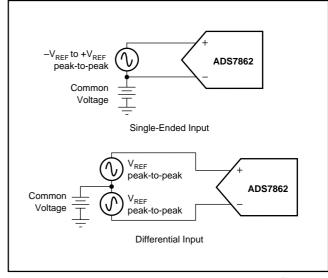

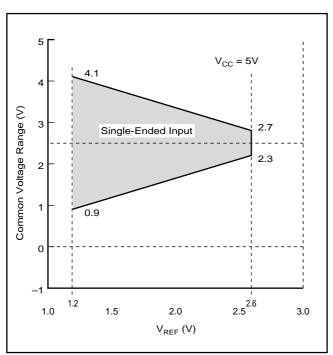

アナログ入力はバイポーラで完全な差動です。ADS7862のアナログ入力をドライブする一般的な方法として、シングルエンドと差動の2つがあります(図1および図2を参照)。入力がシングルエンドのとき、-IN入力は同相モード電圧に保持されます。+IN入力は同じ同相モード電圧を中心にスイングし、ピーク・ツー・ピークの振幅は(同相モード+V<sub>REF</sub>)から(同相モード-V<sub>REF</sub>)までになります。V<sub>REF</sub>の値によって、同相モード電圧の変動する範囲が決まります(図3を参照)。

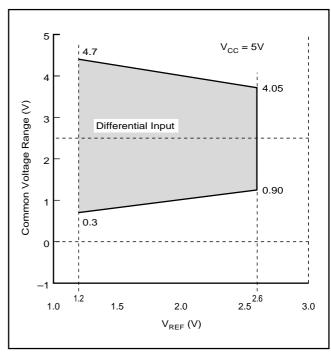

入力が差動のとき、入力の振幅は+INおよび-IN入力の差の (+IN) - (-IN)になります。各入力のピーク・ツー・ピークの振幅は、この同相モード電圧を中心とする $\pm 1/2$ V $_{REF}$ です。ただし、入力の位相が180度ずれているため、差動電圧のピーク・ツー・ピークの振幅は+ $V_{REF}$ から $-V_{REF}$ までになります。 $V_{REF}$ の値によって、両方の入力に共通の電圧の範囲も決まります(図4を参照)。

図1. ADS7862をシングルエンドまたは差動でドライブする方法

図2.シングルエンド入力および差動入力モードでのADS7862の使用

図3.シングルエンド入力:同相モード電圧範囲対 /。。。

図4.差動入力:同相モード電圧範囲対∨<sub>RFF</sub>

いずれの場合も、+INおよび-IN入力をドライブするソースの 出力インピーダンスがマッチングするように注意が必要です。 マッチングしない場合は、温度や入力電圧とともに変化するオフセット誤差の原因になります。

アナログ入力の入力電流は、サンプリング・レート、入力電圧、ソース・インピーダンスなど、多数の要因に依存します。 ADS7862に流れ込む電流は、サンプリング周期の間に内部キャパシタ・アレイを充電します。このキャパシタンスが完全に充電 された後、入力電流は流れなくなります。アナログ入力電圧のソースは、入力キャパシタンス(15pF)を2クロック・サイクル以内に12ビットのセトリング・レベルまで充電できることが必要です。コンパータがホールド・モードに移行すると、入力インピーダンスは $1G\Omega$ より大きくなります。

絶対アナログ入力電圧については注意が必要です。+IN入力は、常にGND-300mVから $V_{DD}+0.3V$ までの範囲に保持することが必要です。

#### トランジション・ノイズ

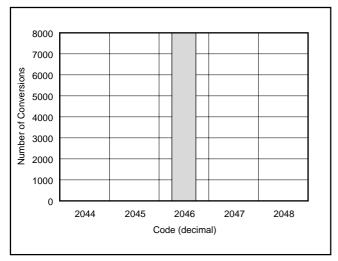

図5に、ADS7862でDC入力の8,000回の変換を実行したときの ヒストグラムを示します。DC入力を出力コード2046に設定して います。1回の変換を除くすべての変換で、出力コード2046の結 果が得られます(1回の変換の出力結果は2047)。ヒストグラム は、ADS7862の優れたノイズ性能を示しています。

図5.DC入力の8,000回の変換のヒストグラム

#### バイポーラ入力

ADS7862の差動入力は、内部リファレンス電圧(2.5V)を中心とする-V<sub>REF</sub>および+V<sub>REF</sub>のバイポーラ入力(2.5Vリファレンスの場合、0Vから5Vまでの入力範囲)を使用できるように設計されています。1個のアンプと4個の外部抵抗からなる簡単なオペアンプ回路を使用して、ADS7862をバイポーラ入力に構成することができます。図7に示す抵抗値の使用により、一般的な±2.5V、±5V、±10Vの入力範囲とADS7862のインターフェースが可能です。

### タイミングおよび制御

ADS7862は、外部クロック(CLOCK、ピン19)を使用して CDACの変換レートを制御します。8MHzの外部クロックを使用 すると、A/Dのサンプリング・レートは、最大スループット時間 2µsに対応する500kHzになります。

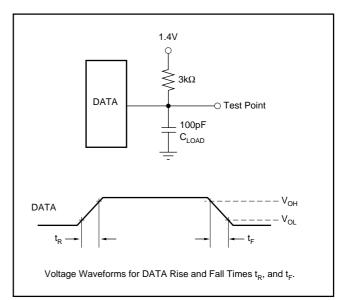

図6.タイミング仕様のテスト回路

図7. バイポーラ入力レンジのレベル・シフト回路

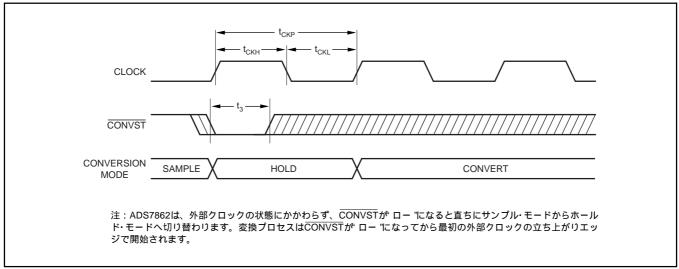

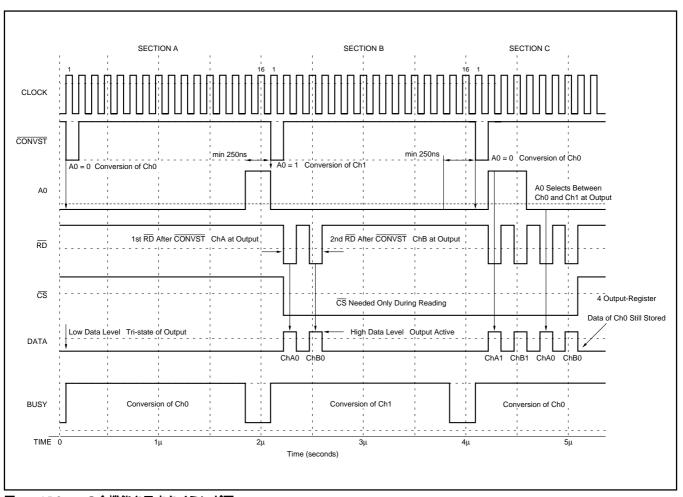

ADS7862の動作を説明するために3つのタイミング図を使用します。図8に、CLOCK、CONVST(ピン18)、および変換モードのタイミングの関係を示します。

図8.変換モード

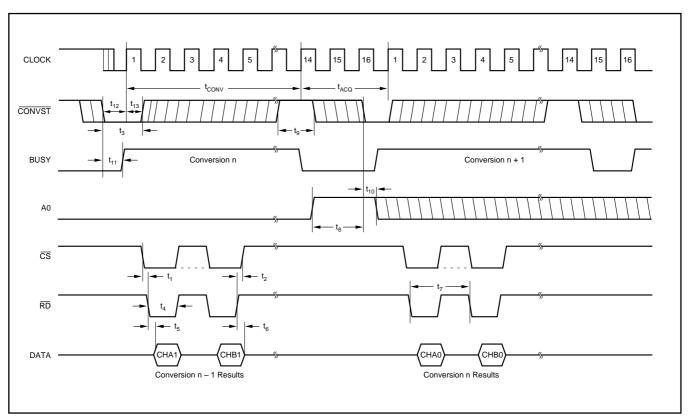

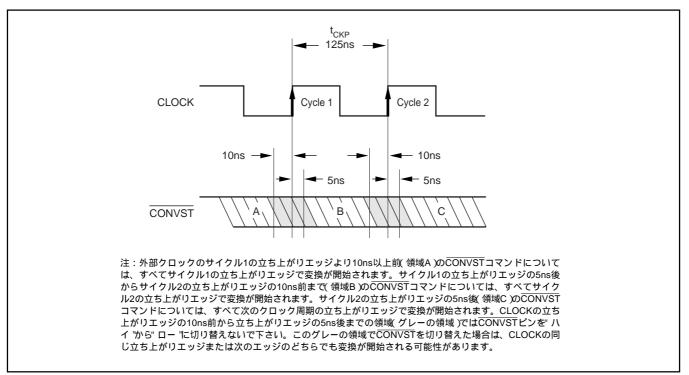

図9に、ADS7862の基本的な読み取り/書き込み機能と、すべてのタイミング仕様を示します(タイミング仕様の表を参照)。図10に、CONVSTを使用した変換開始の詳細を示します。図11に、連続した3回の変換を示し、ADS7862のすべての読み取り/書き込み機能について説明します。

| 説明           | アナログ入力                                     | デジタル出力         |        |  |  |  |

|--------------|--------------------------------------------|----------------|--------|--|--|--|

| フルスケール入力スパン  | $-V_{REF} \sim +V_{RE}^{(1)}$              | パイナリ2の補数       |        |  |  |  |

| 最下位ビット(LSB)  | $(-V_{REF}^{} \sim +V_{REF}^{})4096^{(2)}$ | バイナリ・コード       | 16進コード |  |  |  |

| +フルスケール      | 4.99878V                                   | 0111 1111 1111 | 7FF    |  |  |  |

| ミッドスケール      | 2.5V                                       | 0000 0000 0000 | 000    |  |  |  |

| ミッドスケール–1LSB | 2.49878V                                   | 1111 1111 1111 | FFF    |  |  |  |

| -フルスケール      | 0V                                         | 1000 0000 0000 | 800    |  |  |  |

注: (1)  $N_{REF}$ を中心とする $-V_{REF}$ から $+V_{REF}$ まで。2.5Vリファレンスの場合、入力スパンは0Vから5Vまでになる。(2) 2.5Vリファレンスの場合、1.22mV。

#### 表1.理想的な入力電圧と出力コード

図11のタイミング図は、(A)最初の変換(n-2)の開始、(B)2回目の変換(n-1)の開始と前の変換(n-2)のデータ出力の読み取り、(C)3回目の変換(n)の開始と前2回の変換(n-2およびn-1)の読み取りの3つのセクションに分けることができます。このシーケンスでは、チャンネル0、チャンネル1の順に変換しています。必要な場合は、変換プロセスを開始するときにA0ピンをロジック"ハイ"(チャンネル1)、ロジック"ロー"(チャンネル0)の順に切り替えることにより、チャンネル1、チャンネル0の順に変換することができます。

#### タイミング仕様

| 記号                | 説明                               | 最小  | 標準 | 最大   | 単位 |

|-------------------|----------------------------------|-----|----|------|----|

| t <sub>conv</sub> | 変換時間                             |     |    | 1.75 | μs |

| tACQ              | アクイジション時間                        |     |    | 0.25 | μs |

| t <sub>CKP</sub>  | クロック周期                           | 125 |    | 5000 | ns |

| t <sub>CKL</sub>  | クロック" ロー "                       | 40  |    |      | ns |

| t <sub>CKH</sub>  | クロック" ハイ "                       | 40  |    |      | ns |

| t <sub>1</sub>    | CSからRDまでのセットアップ時間                | 0   |    |      | ns |

| t <sub>2</sub>    | CSからRDまでのホールド時間                  | 0   |    |      | ns |

| t <sub>3</sub>    | CONVST" □ — "                    | 15  |    |      | ns |

| t <sub>4</sub>    | RDパルス幅                           | 30  |    |      | ns |

| t <sub>5</sub>    | RDからデータ有効まで( バスのアクセス )           |     | 16 | 25   | ns |

| t <sub>6</sub>    | RDからハイ・インピーダンスまでの<br>遅延(バスの解放)   |     | 10 | 20   | ns |

| t,                | 変換の読み取りと読み取りの間の時間                | 40  |    |      | ns |

| t <sub>s</sub>    | アドレス・セットアップ時間                    | 250 |    |      | ns |

| t <sub>9</sub>    | CONVST" ハイ "                     | 20  |    |      | ns |

| t <sub>10</sub>   | アドレス・ホールド時間                      | 20  |    |      | ns |

| t <sub>11</sub>   | CONVSTからBUSYまでの伝搬遅延              |     |    | 30   | ns |

| t <sub>12</sub>   | CLOCKの立ち上がりエッジ前の<br>CONVST" ロー " | 10  |    |      | ns |

| t <sub>13</sub>   | CLOCKの立ち上がりエッジ後の<br>CONVST" ロー " | 5   |    |      | ns |

| t <sub>F</sub>    | データ立ち下がり時間                       |     | 13 | 25   | ns |

| t <sub>R</sub>    | データ立ち上がり時間                       |     | 20 | 30   | ns |

図9.同じサイクルのADS7862の読み取りと書き込み

図10.変換を開始するためのCLOCKとCONVSTのタイミング

図11 . ADS7862**の全機能を示すタイミング図**

#### セクションA

変換は、CONVST ピン(ピン18)を5ns以上 " ロー " にすること により開始されます(CONVSTピンは、5ns以上の条件を満たし た後、"ハイ"にすることができます)。ADS7862は、CONVST コマンドの立ち下がりエッジでサンプル・モードからホールド・ モードへ切り替わります。CONVSTが"ロー"になってから最 初の外部クロックの立ち上がりエッジの後、変換が開始されま す(この最初の外部クロックの立ち上がりエッジは、クロック・サ イクル1の最初です。ADS7862が1回の変換を完了するには16サ イクルが必要です)。このときに入力チャンネルもラッチされま す。変換前に正しいアドレスを選択するため、CONVSTピンが "ロー"になる250ns前にA0入力(ピン22)を選択することが必要 です。BUSY出力は、CONVSTが"ロー"になった後、直ちに "ハイ"になります。BUSYは、変換プロセスの間"ハイ"に保 持され、変換が終了すると"ロー"に戻ります。CONVSTが最 小時間"ロー"に保持された後、外部クロックの次の立ち上が リエッジに同期してADS7862がホールド・モードから変換モード へ切り替わり、変換 "n-2"が開始されます。RD(ピン21)およ びCS(ピン20)は、変換前および変換中にはどちらも"ハイ"に することができますが、出力バスからデータ出力を読み取ると きは両方とも"ロー"にすることが必要です。

#### セクションB

$\overline{\text{CONVST}}$  ピンの2回目の"八イ"から"ロー"への切り替えにより、変換"n-1"が開始されます。変換の新しいアドレスを確実に選択するため、ここでも $\overline{\text{CONVST}}$ が"ロー"になる250ns前にアドレスを選択することが必要です。パラレル出力バスから変換"n-2"のチャンネルA0の結果を読み取るには、 $\overline{\text{RD}}$  および $\overline{\text{CS}}$  ピンの両方を"ロー"にします。 $\overline{\text{CS}}$  を"ロー"に保持しながら $\overline{\text{RD}}$  を30ns以上"ロー"にすることにより、出力バスから変換"n-2"のチャンネルA0の結果が出力されます。 $\overline{\text{RD}}$  ピンの2回目の"八イ"から"ロー"への切り替えにより、出力バスから変換"n-2"のチャンネルB0の結果が出力されます。

#### セクションC

$\overline{\text{CONVST}}$  の3回目の " ロー " への切り替えにより、変換 " n " (チャンネル0)が開始されます。変換中に変換 " n -2 " と " n -1 " の結果を読み取ることができます。 $\overline{\text{CS}}$  と $\overline{\text{RD}}$  が " ロー " のときにアドレス・ピンを " ハイ " にすることにより、出力バスから変換 " n -1 " のチャンネルA1の結果が出力されます。セクションCの $\overline{\text{RD}}$  ピンの2回目の " ハイ " から " ロー " への切り替えにより、出力バスから変換 " n -1 " のチャンネルB1の結果が出力されます。次に、アドレス・ピン(A0)を " ロー " にすると、チャンネル 0の最新の変換(n -2)について読み取りプロセスが繰り返され、出力バスから結果が出力されます。

#### データの読み取り

ADS7862は、完全なパラレル・データをバイナリ2の補数のデータ出力フォーマットで出力します。パラレル出力は、 (ご(ピン20)と (ピン21)の両方が "ロー"のときアクティブになります。出力データは、 (CONVSTの立ち下がりエッジの125ns前および立ち下がりエッジの10ns後に読み取らないで下さい。これ以外のどの (CSおよび RDの組み合わせでも、パラレル出力はトライステートになります。 有効な変換データは、ピン5から16(MSB – LSB)で読み取ることができます。 理想的な出力コードについては、表を参照して下さい。

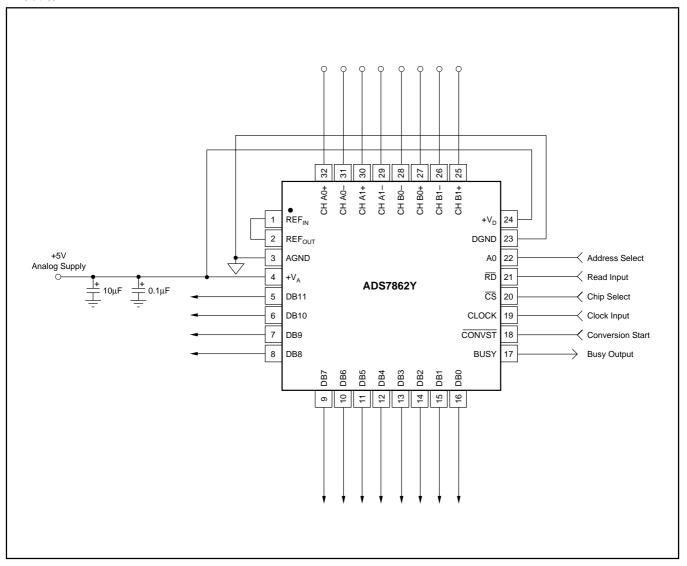

### レイアウト

最適な性能を確保するためには、ADS7862の回路レイアウト に注意することが必要です。クロック入力が最大スループット・ レートに近い場合には特に重要です。

基本的なSARアーキテクチャは、電源、リファレンス、グランド、およびデジタル入力の各端子でアナログ・コンパレータ出力をラッチする直前に発生するグリッチに敏感です。したがって、nビットのSARコンパータの1回の変換には、変換結果が大きな外部過渡電圧に影響される可能性があるn個の「窓」が存在します。このようなグリッチは、スイッチング電源、付近のデジタル・ロジック、ハイパワー・デバイスなどから発生します。デジタル出力の誤差の程度は、リファレンス電圧、レイアウト、および正確な外部イベントのタイミングに依存します。外部イベントとクロック入力のタイミングが変化する場合、誤差が変動します。

このことを考慮して、ADS7862にはクリーンな電源を使用し、十分にパイパスすることが必要です。パッケージのできるだけ近くに0.1µFのパイパス用セラミック・コンデンサを配置します。また、1µFから10µFのコンデンサも推奨されます。必要な場合には、雑音の多い電源のローパスフィルタとして、さらに容量の大きいコンデンサと5Ωまたは10Ωの直列抵抗を使用することができます。ADS7862は、リファレンス電圧が内部でパッファリングされるため、通常は外部リファレンスから電流をほとんど引き込みません。オペアンプが発振なしにバイパス・コンデンサまたはその他のコンデンサをドライブできることを確認して下さい。内部リファレンスを使用する場合、パイパス・コンデンサは不要です(ピン1をピン2に直接接続します)。

AGNDおよびDGNDピンは、クリーンなグランド・ポイントに接続して下さい。これにはすべての場合に"アナログ"グランドを使用します。マイクロコントローラまたはデジタル信号プロセッサのグランド・ポイントと接近しすぎた位置に接続しないで下さい。必要な場合は、コンパータから電源のエントリ・ポイントまで直接グランド・トレースを配置します。コンパータとそのアナログ回路に専用のアナログ・グランド・プレーンを設けたレイアウトが理想的です。

### 外観