# 4チャンネル、16ビット・サンプリングCMOS A/Dコンバータ

# 特長

- サンプリング+変換時間: 25μs(最大)

- ◆ +5∨単一電源動作

- 12ビットADS7824とピン・コンパチブル

- パラレルおよびシリアルデータ出力

- 28ピン0.3インチ幅プラスチックDIPおよび SOP

- 積分直線性誤差±2LSB(最大)

- 消費電力: 50mW(最大)

- パワーダウン・モード:50µW

- 入力レンジ:±10V、4チャンネル入力マルチプレクサ

- 連続変換モード

# 概要

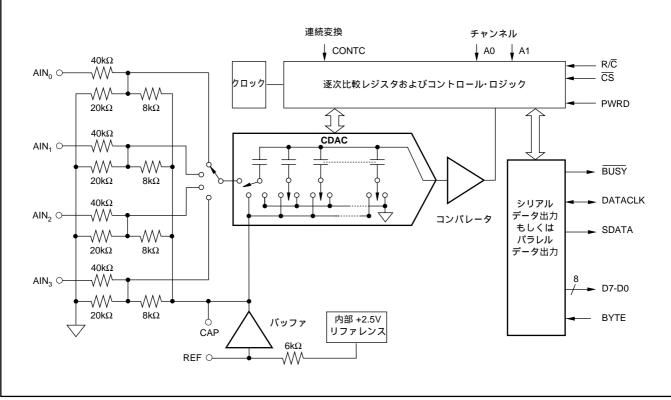

ADS7825は、50mW(最大)の低消費電力ながら25µs(最大)で16ビット±2LSBの精度でアクイジションと変換を実行することができます。レーザ・トリミングされたスケーリング抵抗により工業標準の±10Vの入力レンジおよび±0.1%のチャンネル間マッチングを実現しました。

ADS7825は、ローパワー16ビット・サンプリングA/Dコンパータで、4チャンネルマルチプレクサ、サンプル/ホールド、クロック、リファレンス、パラレル/シリアル・マイクロプロセッサ・インターフェース等A/Dコンパータに必要な全機能を内蔵しています。また、連続変換モードにより4チャンネルのアナログ入力チャンネルを自動的にシーケンシャルに切り替えながらデジタイズすることができます。

ADS7825は、28ピン0.3インチ幅プラスチックDIPおよび SOPで供給され、どちらも-40 から+85 の工業温度範囲 で動作が完全に規定されています。

PDSJ-1304B June, 1996

# 電気的仕様

特に記述がない限り、 $T_a=-40~~+85~~$ 、 $f_s=40$ kHz、 $V_{s,i}=V_{s,o}=V_s=+5$ V $\pm5$ %、外部リファレンス使用、CONTC=0Vです。

|                                                                                                                                                                                                        |                                                                                                                                                                                                   | ,                     | ADS7825P,                   | U                                          | Αſ                 | DS7825PB, I | UB                                |                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------------|--------------------------------------------|--------------------|-------------|-----------------------------------|----------------------------------------------------------|

| パラメータ                                                                                                                                                                                                  | 条件                                                                                                                                                                                                | 最小                    | 標準                          | 最大                                         | 最小                 | 標準          | 最大                                | 単位                                                       |

| 分解能                                                                                                                                                                                                    |                                                                                                                                                                                                   |                       |                             | 16                                         |                    |             | *(1)                              | Bits                                                     |

| <b>アナログ入力</b><br>電圧レンジ<br>インピーダンス<br>容量                                                                                                                                                                | チャンネルオンまたはオフ                                                                                                                                                                                      |                       | ±10V<br>45.7<br>35          |                                            |                    | * *         |                                   | V<br>kΩ<br>pF                                            |

| スループット速度<br>変換時間<br>アクイジション時間<br>マルチプレクサ・セトリング時間<br>完全サイクル(アクイジションおよび変換)<br>完全サイクル(アクイジションおよび変換)<br>スループット・レート                                                                                         | アクイジションを含む<br>CONTC = +5V                                                                                                                                                                         | 40                    | 20<br>5<br>5                | 25<br>40                                   | *                  | * *         | *                                 | μs<br>μs<br>μs<br>μs<br>μs<br>kHz                        |

| DC <b>精度</b><br>積分直線性誤差<br>ノーミッシング・コード<br>トランジション・ノイズ <sup>(3)</sup><br>フルスケール誤差 <sup>(4)</sup><br>フルスケール誤差 <sup>(4)</sup><br>フルスケール誤差 ドリフト<br>バイポーラ・ゼロ誤差<br>バイポーラ・ゼロ誤差<br>ドリフト<br>チャンネル間ミスマッチ<br>電源感度 | 内部リファレンス<br>内部リファレンス<br>+4.75 < V <sub>s</sub> <+5.25                                                                                                                                             | 15                    | 0.8<br>±7<br>±2<br>±2       | ±3<br>±0.5<br>±0.5<br>±10<br>±0.1<br>±8    | 16                 | * ±5 * *    | ±2<br>±0.25<br>±0.25<br>*<br>±0.1 | LSB <sup>(2)</sup> LSB % ppm/°C % ppm/°C mV ppm/°C % LSB |

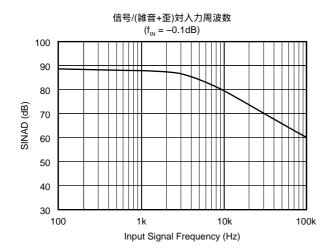

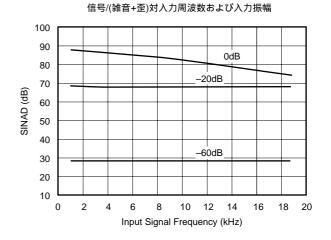

| AC精度<br>スプリアスフリー・ダイナミック・レンジ <sup>(6)</sup><br>全高調波歪(THD)<br>信号/(雑音+歪)比(SINAD)<br>信号/雑音比(SNR)<br>チャンネル・セパレーション <sup>(6)</sup><br>- 3dB帯域幅<br>有効帯域幅 <sup>(7)</sup>                                       | $\begin{aligned} &f_{_{\rm IN}} = 1 \text{kHz} \\ &f_{_{\rm IN}} = 1 \text{kHz} \end{aligned}$ | 90<br>83<br>83<br>100 | 120<br>2<br>90              | -90                                        | *<br>86<br>86<br>* | * *         | *                                 | dB<br>dB<br>dB<br>dB<br>dB<br>MHz<br>kHz                 |

| <b>サンプリングのダイナミック特性</b><br>アパーチャ遅延<br>過電圧復帰 <sup>(6)</sup><br>過負荷回復時間 <sup>(6)</sup>                                                                                                                    | FS ステップ                                                                                                                                                                                           |                       | 40<br>5<br>1                |                                            |                    | * * *       |                                   | ns<br>μs<br>μs                                           |

| リファレンス<br>内部リファレンス電圧<br>内部リファレンス・ソース電流<br>(外部バッファを使用しなければなりません)<br>直線性仕様を満たす<br>外部リファレンス電圧範囲<br>外部リファレンス電流ドレイン                                                                                         |                                                                                                                                                                                                   | 2.48                  | 2.5<br>1<br>2.5             | 2.52<br>2.7<br>100                         | *                  | *           | *                                 | V<br>μΑ<br>V<br>μΑ                                       |

| デジタル入力<br>ロジック・レベル<br>V <sub>IL</sub><br>V <sub>IH</sub><br>I <sub>IL</sub><br>I <sub>IH</sub>                                                                                                         | V <sub>REF</sub> = +2.5V                                                                                                                                                                          | -0.3<br>+2.4          |                             | +0.8<br>V <sub>s</sub> +0.3V<br>±10<br>±10 | *                  |             | * * * *                           | ν<br>ν<br>μΑ<br>μΑ                                       |

| <b>デジタル出力</b><br>データ・フォーマット<br>データ・コーディング<br>V <sub>OL</sub><br>V <sub>OH</sub><br>リーケージ電流<br>出力容量                                                                                                     | I <sub>SINK</sub> = 1.6mA<br>I <sub>SOURCE</sub> = 500μA<br>ハイ・インビーダンス状態、V <sub>OUT</sub> = 0V ~ V <sub>S</sub><br>ハイ・インピーダンス状態                                                                   | シリフ<br>+4             | ラレル、2バ·<br>Pル、2の補数<br> <br> |                                            | *                  | *           | * *                               | V<br>V<br>μA<br>pF                                       |

このデータシートに記載されている情報は、信頼しうるものと考えておりますが、不正確な情報や、記載漏れ等に関して弊社は責任を負うものではありません。 情報の使用について弊社は責任を負えませんので、各ユーザーの責任においてご使用下さい。価格や仕様は予告なしに変更される場合がありますのでご了承下さい。ここに記載されているいかなる回路についても工業所有権その他の権利またはその実施権を付与したり承諾したりするものではありません。弊社は弊社製品を生命維持に関する機器またはシステムに使用することを承認しまたは保証するものではありません。

# 電気的仕様(続き)

特に記述がない限り、 $T_a=-40~~+85~~$ 、 $f_s=40$ kHz、 $V_{s_1}=V_{s_2}=V_s=+5$ V±5%外部リファレンス使用、CONTC=0Vです。

|                                                                                    |                                                      | ,          | ADS7825P, I | U               | AD | S7825PB, L | JB  |                        |

|------------------------------------------------------------------------------------|------------------------------------------------------|------------|-------------|-----------------|----|------------|-----|------------------------|

| パラメータ                                                                              | 条件                                                   | 最小         | 標準          | 最大              | 最小 | 標準         | 最大  | 単位                     |

| デジタル・タイミング<br>バス・アクセス時間<br>バス開放時間<br>データ・クロック<br>内部クロック<br>(データ送信時のみに出力)<br>外部クロック | PAR/SER = +5V PAR/SER = +5V PAR/SER = 0V EXT/INT LOW | 0.5        |             | 83<br>83<br>1.5 | *  |            | * * | ns<br>ns<br>MHz<br>MHz |

| <b>電源</b><br>V <sub>S1</sub> = V <sub>S2</sub> = V <sub>S</sub><br>消費電力            | f <sub>s</sub> = 40kHz<br>PWRD HIGH                  | +4.75      | +5<br>50    | +5.25<br>50     | *  | *          | *   | V<br>mW<br>μW          |

| 温度範囲<br>仕様に規定された性能<br>保存<br>熱抵抗 $(\theta_{\rm JA})$<br>プラスチックDIP<br>SOP            |                                                      | -40<br>-65 | 75<br>75    | +85<br>+150     | *  | *          | *   | °C/W<br>°C/W<br>°C     |

注:(1)\*は左側のグレードと仕様が同じであることを示します。(2)LSBは最下位ビットを意味します。16ビット±10V入力レンジの場合、1LSBは305μVです。(3)ワーストケースのトランジションおよび温度における標準的なrms ノイズ。(4)フルスケール誤差は、トリムされない・フルスケールまたは+フルスケールのワーストケース値と理想的な最初および最後のコード・トランジションとの偏差をトランジション電圧で除算(フルスケール・レンジで除算しない)した値で、オフセット誤差の影響が含まれます。(5)単位がdBのすべての仕様はフルスケール±10V入力を基準にしています。(6)1つのチャンネル上のフルスケール正弦波入力が他チャンネル上で減衰される量を示します。(7)有効帯域幅は信号/(雑音+歪)比が60dBまたは10ビット精度に低下したときのフルスケール入力周波数で定義されます。(8)ステップ後にフル・アクイジション期間を与えれば、どの様な入力ステップに対しても正確にアクイジションを行います。(9)フルスケールの2倍の過電圧が印加された後、仕様に規定される性能に復帰するまでの回復時間。

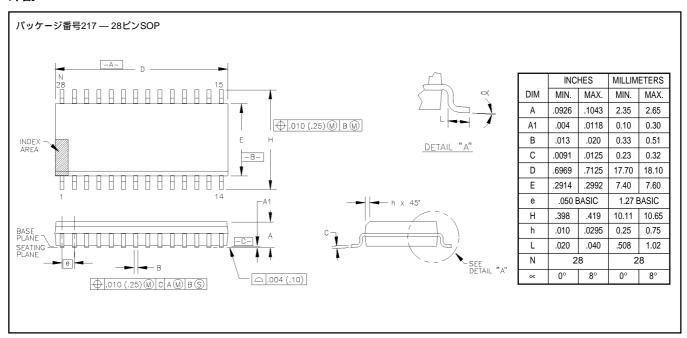

## ご発注の手引き/パッケージ情報

| モデル       | パッケージ     | パッケージ<br>図番号 <sup>(1)</sup> | 温度範囲          | 最大積分<br>直線性誤差(LSB) | 最小信号/<br>( <b>雑音 + 歪)比</b> (dB) |

|-----------|-----------|-----------------------------|---------------|--------------------|---------------------------------|

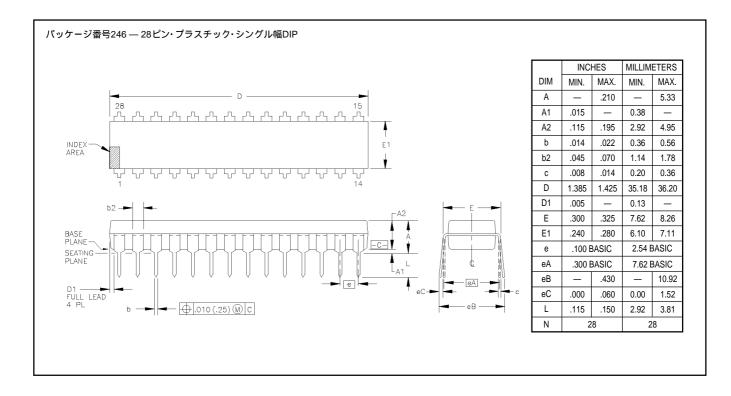

| ADS7825P  | プラスチックDIP | 246                         | -40°C ~ +85°C | ±3                 | 83                              |

| ADS7825PB | プラスチックDIP | 246                         | -40°C ~ +85°C | ±2                 | 86                              |

| ADS7825U  | SOP       | 217                         | -40°C ~ +85°C | ±3                 | 83                              |

| ADS7825UB | SOP       | 217                         | -40°C ~ +85°C | ±2                 | 86                              |

注:(1)詳細図および寸法表については、データシートの巻末を参照して下さい。

### 絶対最大定格

| アナログ入力 AIN <sub>0</sub> 、AIN <sub>1</sub> 、AIN <sub>2</sub> 、AIN <sub>3</sub><br>REF | $(AGND2-0.3V) \sim (V_s+0.3V)$ |

|--------------------------------------------------------------------------------------|--------------------------------|

| CAP                                                                                  | AGND2への無制限の短絡                  |

|                                                                                      | V <sub>s</sub> への瞬時短絡          |

| V <sub>s1</sub> およびV <sub>s2</sub> からAGND2                                           | 7V                             |

| V <sub>s1</sub> からV <sub>s2</sub>                                                    | ±0.3V                          |

| AGND1、AGND2およびDGND間の電圧差                                                              | ±0.3V                          |

| デジタル入力および出力                                                                          | 0.3V ~ (V <sub>S</sub> +0.3V)  |

| 最大接合部温度                                                                              | 150                            |

| 内部消費電力                                                                               |                                |

| リード温度(10秒間の半田付け)                                                                     | +300                           |

| 最大入力電流(全てのピンにおいて)                                                                    |                                |

# 静電気放電対策

静電気放電はわずかな性能の低下から完全なデバイスの故障に 至るまで、様々な損傷を与えます。すべての集積回路は、適切な ESD保護方法を用いて、取扱いと保存を行うようにして下さい。 高精度の集積回路は、損傷に対して敏感であり、極めてわずかな パラメータの変化により、デバイスに規定された仕様に適合しな くなる場合があります。

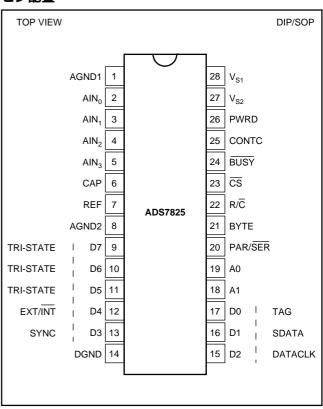

### ピン配置

# ピン構成

| ピン# | 記号               | I/O | 説明                                                                                                                                                                                        |

|-----|------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | AGND1            |     | アナログ・グランド。内部でグランド・リファレンス・ポイントとして使用。                                                                                                                                                       |

| 2   | AIN <sub>o</sub> |     | アナログ入力チャンネル0。フルスケール入力範囲;±10V                                                                                                                                                              |

| 3   | AIN₁             |     | アナログ入力チャンネル1。フルスケール入力範囲;±10V                                                                                                                                                              |

| 4   | AIN <sub>2</sub> |     | アナログ入力チャンネル2。フルスケール入力範囲;±10V                                                                                                                                                              |

| 5   | AIN <sub>3</sub> |     | アナログ入力チャンネル3。フルスケール入力範囲;±10V                                                                                                                                                              |

| 6   | CAP              |     | 内部リファレンス・バッファ出力。2.2μFタンタル・コンデンサをグランドとの間に接続する。                                                                                                                                             |

| 7   | REF              |     | リファレンス入出力。公称電圧+2.5Vを出力。外部で使用する場合はADS7825の精度を保つためバッファを使用しなければなりません。外部のシステム・リファレンスでドライブすることがが可能。どちらの場合にも、2.2μFタンタル・コンデンサを使用してバイパスにグランドする。                                                   |

| 8   | AGND2            |     | アナログ・グランド                                                                                                                                                                                 |

| 9   | D7               | 0   | PAR/SERが ハイ "の場合は、パラレル・データ・ビット7。PAR/SERが ロー "の場合は、トライステート状態になる。表lを参照。                                                                                                                     |

| 10  | D6               | 0   | PAR/SERが ハイ "の場合は、パラレル・データ・ビット6。PAR/SERが ロー "の場合は、トライステート状態になる。表Iを参照。                                                                                                                     |

| 11  | D5               | 0   | PAR/SERが ハイ 'の場合は、パラレル・データ・ビット5。PAR/SERが ロー 'の場合は、トライステート状態になる。表lを参照。                                                                                                                     |

| 12  | D4               | I/O | PAR/SERが ハイ 'の場合は、パラレル・データ・ビット4。PAR/SERが ロー 'の場合は内部シリアル・クロックを使用して前に変換<br>したシリアルデータをSDATAに送信する。" ハイ 'の場合はDATACLK(D2)ピンに入力される外部シリアル・クロックを使用してシリ<br>アルデータを送信する。表Iを参照。                        |

| 13  | D3               | 0   | PAR/SERが ハイ "の場合は、パラレルデータ・ビット3。 PAR/SERが ロー "の場合はSYNCを出力。表Iを参照。                                                                                                                           |

| 14  | DGND             |     | デジタル・グランド。                                                                                                                                                                                |

| 15  | D2               | I/O | PAR/SERが ハイ 'の場合は、パラレルデータ・ビット2。 PAR/SERが ロー "でEXT/INT(D4)が ロー "の場合は内部シリアル・クロックを出力。 EXT/INT(D4)が ハイ 'の場合は外部シリアル・クロック用の入力となる。表Iを参照。                                                         |

| 16  | D1               | 0   | PAR/SERが、ハイ "の場合はパラレルデータ・ビット1。PAR/SERが ロー "の場合にはSDATAシリアルデータ出力。表Iを参照。                                                                                                                     |

| 17  | D0               | I/O | PAR/SERが、ハイ "の場合はパラレルデータ・ビット0。PAR/SERが ロー "の場合にはTAGデータ入力。表Iを参照。                                                                                                                           |

| 18  | A1               | I/O | CONTCが ロー "の場合にはチャンネル・アドレス入力、CONTCが ハイ "の場合にはチャンネル・アドレス出力。表Iを参照                                                                                                                           |

| 19  | A0               | I/O | CONTCが ロー 'の場合にはチャンネル・アドレス入力、CONTCが ハイ 'の場合にはチャンネル・アドレス出力。表Iを参照                                                                                                                           |

| 20  | PAR/SER          | 1   | パラレルまたはシリアル出力を選択。" ハイ 'の場合にはパラレルデータは、D7からD0に出力される。" ロー 'の場合には、シリアルデータがSDATAに出力される。 表Iおよび図1を参照                                                                                             |

| 21  | BYTE             | I   | バイト選択。PAR/SERが ハイ "となるパラレルデータのみに使用される。CSが ロー "でR/Cを" ハイ "にすると、BYTEによりデータ・<br>パスを切り替えることができます。" ロー "では、8MSBを選択し、" ハイ "では8LSBsを選択します。図2および図3を参照。                                            |

| 22  | R/C              | I   | リード/変換入力。CS' ロー "では、R/Cの立ち下がりエッジは、内部サンプル/ホールドをホールド状態にし、変換を開始する。CSが<br>"ロー "でPAR/SERが ハイ "の場合には、R/Cの立ち上がりエッジはデータ出力ビットをイネーブルに、PAR/SERが ロー "の場合お<br>よびEXT/INTが" ハイ "の場合にはシリアルデータの送信を開始する。    |

| 23  | CS               | I   | チップ選択。内部でR/CとOR接続される。CONTCが ロー "でR/Cが ロー "の場合にはCSの立ち下がリエッジで新いい変換が開始され、R/Cが ハイ "のとき、PAR/SERが ハイ "ならば出力データ・ビットは、CSの立ち下がリエッジでイネーブルになるか、またはPAR/SERが ロー "でEXT/INTが ハイ "の場合には、シリアルデータの送信が開始される。 |

| 24  | BUSY             | 0   | BUSY出力。変換が開始されると立ち下がり、変換が完了してデータが出力レジスタにラッチされるまで、"ロー "を保持する。バラレル出力モードではBUSYが立ち上がると出力データが有効になるため、データをラッチするために立ち上がりエッジを使用することができる。                                                          |

| 25  | CONTC            | I   | 連続変換入力。"ロー 'の場合は、CSとR/Cを使用してノーマルな変換を行う。変換はノーマルに発生し、" ハイ 'の場合は連続変換<br>モードによりCS、R/CおよびPWRDが、" ロー 'の間は4つの入力チャンネルすべてを自動的にシーケンシャルに切り替えながらアク<br>イジションと変換を連続的に行う。シリアルモードのみの場合は表Iを参照。             |

| 26  | PWRD             | I   | パワーダウン入力。" ハイ 'の場合には、変換が禁止され、消費電力が大きく減少する。前の変換の結果は、出力レジスタに保持される。 連続変換モードでは、マルチプレクサ・アドレス・チャンネルは、チャンネル0にリセットされる。                                                                            |

| 27  | V <sub>s2</sub>  |     | 電源入力。公称+5V。ピン28に直接接続する。0.1μFセラミックおよび10μFタンタル・コンデンサでデカップリングしてください。                                                                                                                         |

| 28  | V <sub>s1</sub>  |     | 電源入力。公称+5V。ピン27に直接接続する。                                                                                                                                                                   |

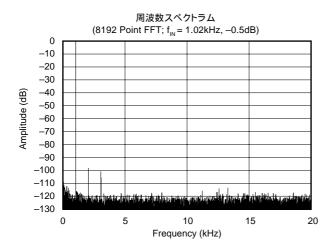

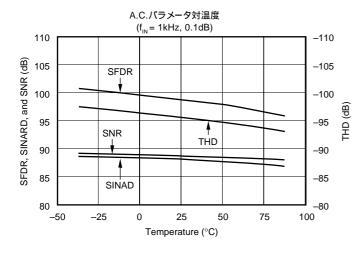

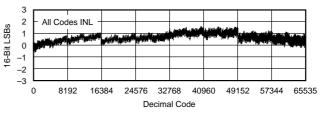

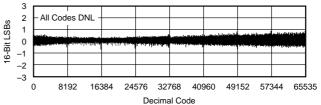

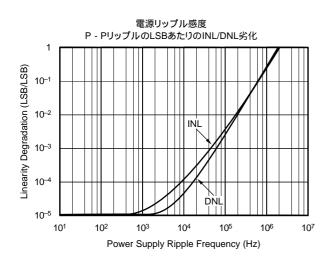

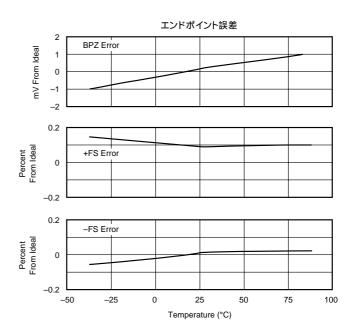

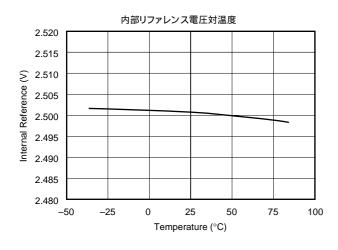

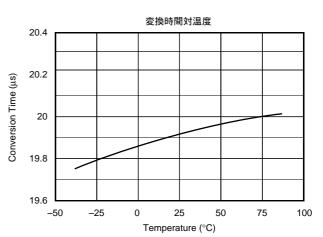

# 代表的性能曲線

特に記述がない限り、 $T_a$ =+25、 $f_s$ =40 kHz、 $V_{s_1}$  =  $V_{s_2}$ =+5V、内部リファレンスを使用。

# 代表的性能曲線

特に記述のない限り、 $T_A$  = +25 、  $f_S$  = 40kHz、 $V_{S1}$  =  $V_{S2}$  = +5V、内部リファレンスを使用。

# 基本操作

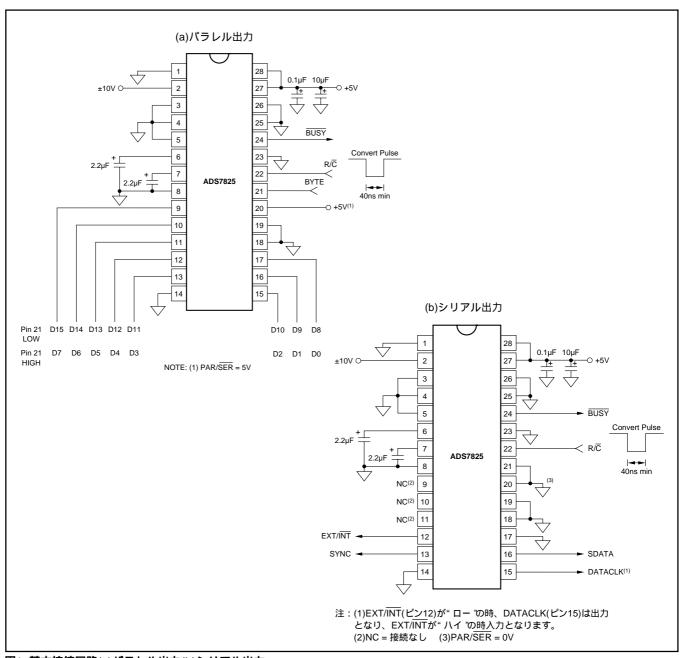

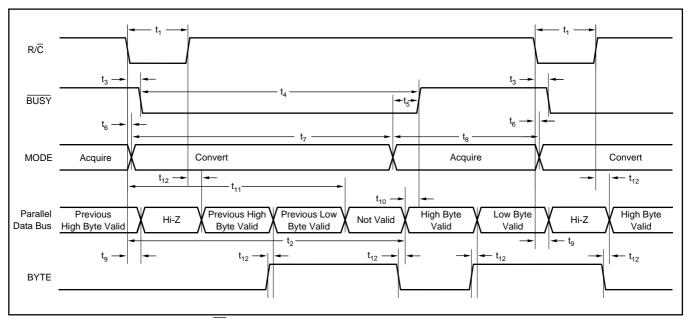

#### パラレル出力

図1aに、ADS7825をパラレル出力(チャンネル0を選択)で操作する場合の基本回路を示します。R/C(ピン22)を最低40ns(最大12μs) "ロー"にすることによって変換が開始され、BUSY(ピン24)が"ロー"になります。BUSYは変換が完了し出力レジスタが更新されるまで"ロー"を維持します。BYTE(ピン21)が"ロー"の場合、ピン24が立ち上がる時に最上位8ピットが有効になります。BYTEが"ハイ"の場合、BUSYが立ち上がる時に最下位8ピットが有効になります。データは2の補数パイナリ・フォーマットで出力されます。BUSYが"ハイ"になるとデータをラッチすることができます。最初のパイトが読まれた後、BYTEはトグルすることができ残りのパイトを読むことが可能になります。BUSYが"ロー"の間は、すべての変換コマンドが無視されます。

ADS7825は変換の終了時に入力信号のトラッキングを開始します。新しい信号の正確なアクイジションを保証するためには、変換コマンド間に25μsを与える必要があります。

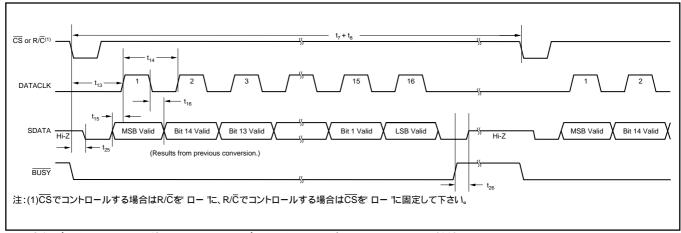

### シリアル出力

図1bに、ADS7825をシリアル出力(チャンネル0を選択)で操作する場合の基本回路を示します。R/C(ピン22)を最低40ns(最大12μs) "ロー"にすることによって変換が開始され、DATACLK(ピン15)に出力される16個のクロック・パルスに同期して、前の変換からの有効データがSDATA(ピン16)に出力されます。BUSY(ピン24)は"ロー"になり、変換が完了しシリアル・データが送信されるまで"ロー"を維持します。データは2の補数パイナリ・フォーマット、MSBファーストで出力されます。またデータはデータ・クロックの立ち上がリエッジと立ち下がリエッジの両方で有効になります。BUSYが"ハイ"になるとデータをラッチするのに使用することができます。BUSYが"ロー"の間は、すべての変換コマンドが無視されます。

ADS7825は変換の終了時に入力信号のトラッキングを開始します。新しい信号の正確なアクイジションを保証するためには、変換コマンド間に25μsを与える必要があります。

図1. 基本接続回路(a)パラレル出力(b)シリアル出力

# 変換の開始

でS(ピン23)とR/で(ピン22)が最低40nsの間"ロー"になると、直ちにADS7825のサンプル/ホールドがホールド状態になり変換"n"が開始されます。変換が開始されると、BUSY(ピン24)は"ロー"になり変換"n"が完了し内部出力レジスタが更新されるまで"ロー"が保持されます。BUSYが"ロー"の間はすべての新しい変換コマンドが無視されます。新しい信号をアクイジションする時間が十分にないまま新しい変換が開始されてしまうので、でSとR/で、あるいはでSまたはR/では、BUSYが"ハイ"になる前に"ハイ"にならなければなりません。

ADS7825は、変換の終了時に入力信号のトラッキングを開始します。新しい信号の正確なアクイジションを保証するためには、変換コマンド間に25μsを与える必要があります。表laおよび表lbでCS、R/C、およびBUSYの状態を参照して下さい。また図2から図6および表のタイミング図を参照してください。CSおよびR/Cは内部でOR接続されておりレベル・トリガされます。変

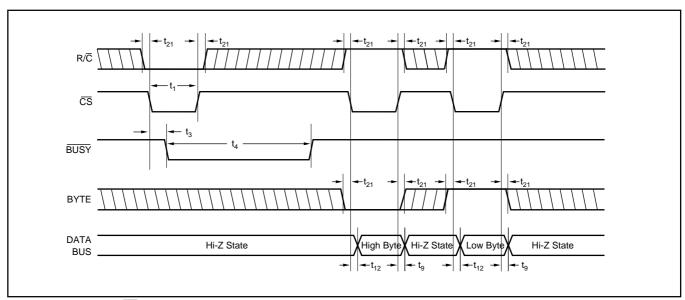

制御ピンの数を減らすためには、R/Cをリードおよび変換モードの制御に使用してCSを"ロー"に接続することができます。これはシリアル出力モードで内部データ・クロックを使用している場合には問題ありませんが、パラレル出力とシリアル出力(外部データ・クロックを使用している場合のみ)はR/Cが"ハイ"になるたびに影響を受けます。データのリードの項および図2、図3、図5、図6を参照してください。

|    |     | λ    | カ     |      |      | 出力           |                      |      |      |      |                      |                      |             |                   |

|----|-----|------|-------|------|------|--------------|----------------------|------|------|------|----------------------|----------------------|-------------|-------------------|

| cs | R/C | BYTE | CONTC | PWRD | BUSY | D7           | D6                   | D5   | D4   | D3   | D2                   | D1                   | D0          | 動作                |

| 1  | Х   | Х    | Х     | Х    | Х    | Hi-Z         | Hi-Z                 | Hi-Z | Hi-Z | Hi-Z | Hi-Z                 | Hi-Z                 | Hi-Z        |                   |

| X  | 0   | X    | X     | X    | X    | Hi-Z         | Hi-Z                 | Hi-Z | Hi-Z | Hi-Z | Hi-Z                 | Hi-Z                 | Hi-Z        | 目後の本投ウスからの        |

| 0  | 1   | 0    | X     | Х    | ×    | D15<br>(MSB) | D14                  | D13  | D12  | D11  | D10                  | D9                   | D8          | 最後の変換完了からの<br>結 果 |

| 0  | 1   | 1    | Х     | Χ    | Х    | D7           | D6                   | D5   | D4   | D3   | D2                   | D1                   | D0<br>(LSB) | 最後の変換完了からの<br>結 果 |

| 0  | 1   | х    | х     | Х    | 1    | ↑↓           | $\uparrow\downarrow$ | ↑↓   | ↑↓   | ↑↓   | $\uparrow\downarrow$ | $\uparrow\downarrow$ | ↑↓          | データは変換の終了時で変更。    |

表la. パラレルデータ用リード制御(PAR/SER = 5V)

|          |          |       |      |          |          | D4      | D3     | D2      | D1     | D0    |                                                                          |

|----------|----------|-------|------|----------|----------|---------|--------|---------|--------|-------|--------------------------------------------------------------------------|

| CS       | R/C      | CONTC | PWRD | BUSY     | D7,D6,D5 | EXT/INT | SYNC   | DATACLK | SDATA  | TAG   |                                                                          |

| 入力       | 入力       | 入力    | 入力   | 出力       | 出力       | 入力      | 出力     | I/O     | 出力     | 入力    | 動作                                                                       |

| 1        | Х        | Х     | Х    | 1        | Hi-Z     | LOW     | LOW    | Output  | Hi-Z   | Х     |                                                                          |

| X        | 0        | Х     | Х    | 1        | Hi-Z     | LOW     | LOW    | Output  | Hi-Z   | Х     |                                                                          |

| 0        | <b>\</b> | 0     | Х    | 1        | Hi-Z     | LOW     | LOW    | Output  | Output | Х     | DATACLKの16パルス出力に同期してSDATA上<br>に前の変換からのデータを送信開始。                          |

| <b>\</b> | 0        | 0     | Х    | 1        | Hi-Z     | LOW     | LOW    | Output  | Output | Х     | DATACLKの16パルス出力に同期してSDATA上<br>に前の変換からのデータを送信開始。                          |

| 0        | 1        | 0     | Х    | Х        | Hi-Z     | HIGH    | LOW    | Input   | Output | Input | SDATAの出力レベルはTAGの16DATACLK入<br>力サイクルにおける入力レベルと同じになる。                      |

| 0        | 1        | 0     | Х    | 1        | Hi-Z     | HIGH    | LOW    | Input   | Output | Input | 変換終了時に、BUSY の立ち上がりで、変換データが出力レジスタにシフトされる。 もしDATACLKが ハイ "であれば有効なデータが失われる。 |

| 0        | <b>↑</b> | 0     | х    | 1        | Hi-Z     | HIGH    | LOW    | Input   | Output | Х     | SYNCの" ハイ "パルスに続き、DATACLK入力に<br>同期してS D A T A の変換終了データ転送を初期<br>化する。      |

| <b>\</b> | 1        | 0     | Х    | 1        | Hi-Z     | HIGH    | LOW    | Input   | Output | X     | SYNCの" ハイ "パルスに続き、DATACLK入力に<br>同期してS D A T A の変換終了データ転送を初期<br>化する。      |

| 0        | 0        | 1     | 0    | <b>\</b> | Hi-Z     | LOW     | LOW    | Output  | Output | Х     | DATACLKの16パルス出力に同期してSDATAに<br>前の変換からのデータ送信を開始する。                         |

| <b>\</b> | 1        | Х     | Х    | Х        | Hi-Z     | HIGH    | Output | Input   | Output | Х     | SDATAはアクティブになる。DATACLKの入力に<br>よりデータがシフトアウトされる。                           |

| 0        | <b>↑</b> | Х     | Х    | Х        | Hi-Z     | HIGH    | Output | Input   | Output | Х     | SDATAはアクティブになる。DATACLKの入力に<br>よりデータがシフトアウトされる。                           |

| <b>\</b> | 0        | 1     | Х    | Х        | Hi-Z     | LOW     | LOW    | Output  | Output | Х     | 連続変換モードが再開。(BUSYが ロー 'の場合<br>n−1データが送信)。                                 |

| 0        | <b>↓</b> | 1     | Х    | Х        | Hi-Z     | LOW     | LOW    | Output  | Output | Х     | 連続変換モードが再開。(BUSYが ロー "の場合<br>n-1データが送信)。                                 |

表lb. **シリアルデータ用リード制御**(PAR/SER = 0V)

図2. パラレル出力での変換タイミング (CSを"ロー"に接続)

図3. パラレル出力でのCSによる変換とリード・タイミングのコントロール。

図4. 内部データ・クロックを使用するシリアルデータ・タイミング(TAGを"ロー"に接続)

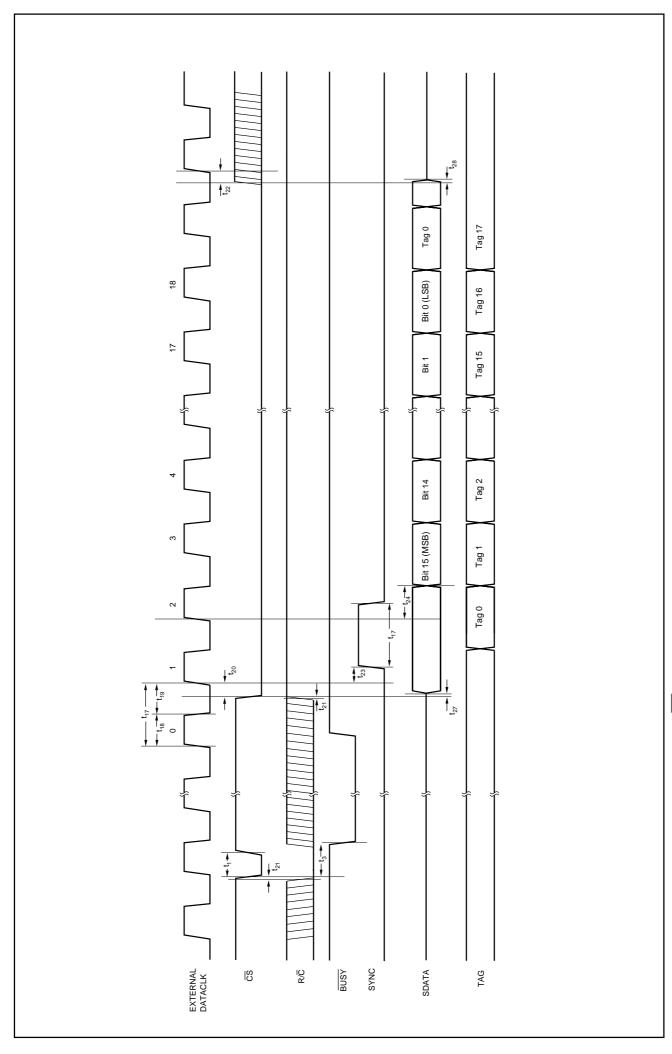

図5. 外部クロックを使用した変換およびリードタイミング (EXT/INTは"ハイ"に接続)。変換後のリード

図6. 外部クロックを使用した変換およびリードタイミング (EXT/INTは"ハイ"に接続)。変換中にリード(前回変換の結果)

# データのリード

### パラレル出力

パラレル出力を使用する場合は、PAR/SER(ピン20)を"ハイ"に接続して下さい。R/C(ピン22)が"ハイ"でCS(ピン23)が"ロー"の時、パラレル出力がアクティブになります。これ以外のCSとR/Cの組合せは、パラレル出力をトライステート状態にします。有効な変換データはD7 - D0(ピン9から13、および15から17)で2つの8ピット・パイトで読むことができます。BYTE(ピン21)が"ロー"の場合は、最上位の8ピットが有効になりMSBはD7に位置します。BYTEが"ハイ"の場合は、最下位の8ピットが有効になりLSBはD0に位置します。BYTEは両方のパイトを1変換サイクル内で読み取るためにトグルできます。最初の電源投入時には、パラレル出力データは不定です。

# パラレル出力(変換後)

変換 " n " が完了し出力レジスタが更新されると、BUSY(ピン24)は"ハイ"になります。変換後の有効データはD7 - D0(ピン9から13およびピン15から17)で得られます。BUSYが"ハイ"になるのを利用してデータをラッチすることができます。タイミングの制約は表IIおよび図2、図3を参照して下さい。

## パラレル出力(変換中)

変換 " n " が開始されると、変換開始後12μsまで変換 " n - 1 " の有効データを読むことができます。変換 " n " の開始後12μs以降は無効なデータを読み取る可能性があるのでBUSY(ピン24)が " ハイ " になるまでデータのリードは行わないで下さい。タイミングの制約は表日および図2、図3を参照して下さい。

#### シリアル出力

PAR/ $\overline{\text{SER}}$ (ピン20)が"ロー"の場合、データは内部クロックまたは外部クロックでクロック・アウトすることができます。EXT/ $\overline{\text{INT}}$ (ピン12)が"ロー"の場合には、DATACLK(ピン15)は出力となり、 $\overline{\text{CS}}$ (ピン23)と $\overline{\text{R}}$ / $\overline{\text{C}}$ (ピン22)の状態に関係なく常にアクティブとなります。SDATA出力は、 $\overline{\text{BUSY}}$ (ピン24)が"ロー"の時、アクティブになります。そうでない場合は、トライステート状態となります。EXT/ $\overline{\text{INT}}$ が"ハイ"の場合、DATACLKは入力となります。 $\overline{\text{CS}}$ が"ロー"で $\overline{\text{R}}$ / $\overline{\text{C}}$ が"ハイ"の場合には、SDATA出力はアクティブになります。そうでない場合は、トライステート状態になります。 $\overline{\text{EXT}}$ / $\overline{\text{INT}}$ の状態に関係なく、SYNC(ピン13)は出力で、常にアクティブです。TAG(ピン17)は常に入力です。

#### 内部データ・クロック(変換中)

内部データ・クロックを使用する場合、EXT/INT(ピン12)を "ロー"に接続して下さい。R/C(ピン22)およびCS(ピン23)が "ロー"になると変換 "n"が開始され、内部データ・クロックが 始動します(標準900kHzクロック・レート)。ADS7825は、変換 "n - 1"からの16ピットの有効データを、MSBファーストでSDATA (ピン16)に出力します。このデータはDATACLK(ピン15)に出力された16クロック・パルスに同期化されています。データは内部データ・クロックの立ち上がリエッジと立ち下がリエッジの両方で有効になります。BUSY(ピン24)の立ち上がリエッジはデータをラッチするのに使用できます。16番目のクロック・パルスの後、SDATA は最初のクロック・パルス時にTAG(ピン17)に入力されたロジック・レベルになります。またDATACLKは(16番めのクロック・パルスの後)次の変換が開始されるまで "ロー"が維持されます。

| 記号                              | 説明                                                        | 最小   | 標準  | 最大 | 単位 |

|---------------------------------|-----------------------------------------------------------|------|-----|----|----|

| t,                              | 変換パルス幅                                                    | 0.04 |     | 12 | μs |

| t <sub>2</sub>                  | 変換開始から新しい有効データ                                            |      | 20  | 21 | μs |

| t <sub>3</sub>                  | 変換開始からBUSY "ロー"                                           |      |     | 85 | ns |

| t <sub>4</sub>                  | BUSY " □ - "                                              |      | 20  | 21 | μs |

| t <sub>5</sub>                  | 変換終了からBUSY " ハイ "                                         |      | 90  |    | ns |

| t <sub>6</sub>                  | アパーチャ遅延                                                   |      | 40  |    | ns |

| t <sub>7</sub>                  | 変換時間                                                      |      | 20  | 21 | μs |

| t <sub>8</sub>                  | アクイジション時間                                                 |      | 4   | 5  | μs |

| t <sub>7</sub> + t <sub>8</sub> | スループット時間                                                  |      |     | 25 | μs |

| t <sub>9</sub>                  | バス解放時間                                                    | 10   |     | 83 | ns |

| t <sub>10</sub>                 | データ有効からBUSY "ハイ"                                          | 20   | 60  |    | ns |

| t,1                             | 変換開始から前データの無効                                             | 12   | 20  |    | μs |

| t <sub>12</sub>                 | バスアクセス時間およびBYTE遅延                                         |      |     | 83 | ns |

| t <sub>13</sub>                 | 変換開始からDATACLK遅延                                           |      | 1.4 |    | μs |

| t <sub>14</sub>                 | DATACLK期間                                                 |      | 1.1 |    | μs |

| t <sub>15</sub>                 | データ有効からDATACLK " ハイ "                                     | 20   | 75  |    | ns |

| t <sub>16</sub>                 | DATACLK "ロー " からデータ無効                                     | 400  | 600 |    | ns |

| t <sub>17</sub>                 | 外部DATACLK期間                                               | 100  |     |    | ns |

| t <sub>18</sub>                 | 外部DATACLK "ハイ"                                            | 50   |     |    | ns |

| t <sub>19</sub>                 | 外部DATACLK " ロー "                                          | 40   |     |    | ns |

| t <sub>20</sub>                 | CS " ロー " およびR/C " ハイ " から外部DATACLK " ハイ " (イネーブルクロック)    | 25   |     |    | ns |

| t <sub>21</sub>                 | R/CからCSセットアップ時間                                           | 10   |     |    | ns |

| t <sub>22</sub>                 | CS " ハイ " もしくはR/C " ロー " から外部DATACLK " ハイ " (ディスエーブルクロック) | 25   |     |    | ns |

| t <sub>23</sub>                 | DATACLK"ハイ"からSYNC"ハイ"                                     | 15   |     | 35 | ns |

| t <sub>24</sub>                 | DATACLK " ハイ " から有効データ                                    | 25   |     | 55 | ns |

| t <sub>25</sub>                 | 変換開始からSDATAアクティブ                                          |      |     | 83 | ns |

| t <sub>26</sub>                 | 変換終了からSDATAトライステート                                        |      |     | 83 | ns |

| t <sub>27</sub>                 | CS " ロー " およびR/C " ハイ " からSDATAアクティブ                      |      |     | 83 | ns |

| t <sub>28</sub>                 | CS " ハイ " もしくはR/C " ロー " からSDATAトライステート                   |      |     | 83 | ns |

| t <sub>29</sub>                 | BUSY " ハイ " から有効アドレス                                      |      |     | 20 | ns |

| t <sub>30</sub>                 | 有効アドレスからBUSY "ロー"                                         | 500  |     |    | ns |

表II. 変換、データおよびアドレス・タイミング T<sub>a</sub> = -40 ~+85

BUSYが"ハイ"に戻るとSDATA出力はトライステートになります。タイミングについては表 および図4を参照して下さい。

#### 外部データ・クロック

外部データ・クロックを使用する場合、EXT/INT(ピン12)を "ハイ"に接続して下さい。外部データ・クロックは、データ・クロックとして使用するのみで変換クロックではありません。 ADS7825の出力モードをイネーブルにするには、 CS(ピン23)は "ロー"、R/C(ピン22)は "ハイ"でなければなりません。 DATACLKはデータ・クロック周期全体の20%から70%の間 "ハイ"でなければなりません。またクロックの速度はDCと10MHz の間にすることができます。変換 "n+1"の最中、または変換 "n"が完了した時、変換 "n"からのシリアルデータはSDATA (ピン16)に出力されます。

コンパータの制御を簡素化するには、CSを"ロー"に接続し、変換を開始するのにR/Cを使用して下さい。この簡素化には障害はありませんが、外部データ・クロックを使用する場合には問題が起こる可能性があります。変換"n"の開始から12μs後からBUSYが立ち上がるまでの間の時点で、内部ロジックは変換"n"の結果を出力レジスタにシフトします。この時点でCSが"ロー"、R/Cが"ハイ"、および外部クロックが"ハイ"の場合はデータが失われてしまいます。有効データが失われるのを避けるため、したがってCSが"ロー"の場合は、この期間中R/CとDATACLK、またはR/CかDATACLKは"ロー"でなければなりません。

#### 外部データ・クロック(変換後)

変換 " n " が完了し出力レジスタが更新された時、BUSY(ピン24)は " ハイ " になります。 CSが " ロー " (ピン23)でR/Cが " ハイ"(ピン22)の場合、変換 " n " からの有効データはSDATA(ピン16)に出力され、DATACLK(ピン15)の外部データ・クロック入力に同期化されます。最初の外部データ・クロックの立ち上がリエッジに続く15から35nsまでの間で、SYNC出力ピンは1フルデータ・クロック間(100ns最小) " ハイ " になります。 MSBはセカンド・データ・クロックの立ち上がリエッジの後、25から55nsの間で有効になります。LSBは、データ・クロックの17番目の立ち下がリエッジおよび18番目の立ち上がリエッジで有効になり、SDATA上に現れます。TAG(ピン17)は全ての外部クロック・パルスにおいて、ビットデータを入力することができます。TAGの最初のビッ

トはDATACLKの18番目の立ち下がりエッジと19番目の立ち上がりエッジに同期してSDATAに現れます。そして2番目の入力ビットは19番目の立ち下がりエッジ、および20番目の立ち上がりエッジで有効というように続いていきます。連続したデータ・クロックでは、次の変換からの結果によって内部出力が、レジスタが更新されるまで、TAGデータはSDATAに出力されます。表日および図5を参照して下さい。

### 外部データ・クロック(変換中)

変換"n"が開始されると、変換開始後12μsまで変換"n-1"の有効データを読むことができます。変換"n"の開始後12μs以降は、データを失ってしまうのでBUSY(ピン24)が立ち上がるまでデータをクロック・アウトしないで下さい(注:外部データ・クロックを使用して最高の性能を実現するためには、変換中はデータをクロック・アウトしないで下さい)。非同期のデータ・クロックのスイッチング雑音は、デジタル・フィードスルーを引き起こしコンバータの性能を劣化させます。表日および図6を参照して下さい。

### TAG機能

TAG(ピン17)は、外部または内部データ・クロックに同期化されたシリアルデータを入力します。

外部データ・クロックを使用する場合は、TAGのシリアル・ビット・ストリーム入力は内部出力レジスタが新しい変換結果で更新されるまで、SDATA(ピン16)のLSB出力に続きます。表IIおよび図5、図6を参照して下さい。

内部データ・クロックの1番目の立ち上がリエッジのTAGへのロジック・レベル入力は、有効データの16ビットすべてが出力された後SDATAで有効になります。

# マルチプレクサ・タイミング

4チャンネル入力マルチプレクサは、マニュアルでアドレスされるか、連続変換モードで4チャンネルすべてがシーケンシャルにアドレスされます。

| CONTC | <del>cs</del> | R/C | BUSY | PWRD | A0 <b>および</b> A1 | 動作                                                                                 |

|-------|---------------|-----|------|------|------------------|------------------------------------------------------------------------------------|

| 0     | Х             | Х   | х    | Х    | 入力               | 変換 n+1 'のためのチャンネルをセレクトするためにAOとA1のレベル入力をラッチし変換 n 'を開始する。                            |

| 0     | Х             | X   | 0    | 0    | 入力               | 変換は進行中。新しい変換コマンドは無視される。                                                            |

| 0     | 0             |     | 1    | 0    | 入力               | 前の変換の最初で選択されたチャンネルによる変換を開始する。                                                      |

| 0     |               | 0   | 1    | 0    | 入力               | 前の変換の最初で選択されたチャンネルによる変換を開始する。                                                      |

| 0     | Х             | Х   | Х    | 1    | 入力               | すべてのアナログ機能が停止する。進行中もしくは開始した変換が無意味なデータを発生する。                                        |

| 1     | Х             | Х   | Х    | Х    | 出力               | 変換 n 'の終わり(BUSYの立ち上がり)が内部チャンネルのラッチをインクリメントし、A0およびA1<br>上の変換 n+1 'のチャンネル・アドレスを出力する。 |

| 1     | Х             | X   | 0    | 0    | 出力               | 変換は進行中。                                                                            |

| 1     | 0             |     | 1    | 0    | 出力               | 連続変換プロセスが次の入力チャンネル上でリスタートする。                                                       |

| 1     |               | 0   | 1    | 0    | 出力               | 連続変換プロセスが次の入力チャンネル上でリスタートする。                                                       |

| 1     | Х             | Х   | х    | 1    | 出力               | すべてのアナログ機能が停止する。進行中もしくは開始した変換が無意味なデータを発生する。<br>次の変換に選択された入力チャンネルがAIN。にリセットされる。     |

表III. 変換コントロール

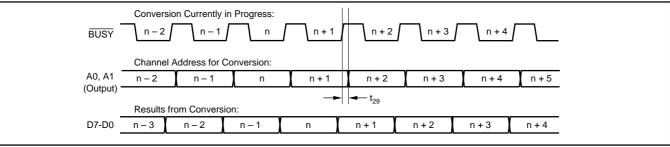

# **連続変換モード**( CONTC=5 V)

ADS7825を連続変換モードにするためには、CONTC(ピン25) を " ハイ " に接続する必要があります。このモードでは、CS、 R/C、PWRDを "ロー "にしている間は全チャンネルのアクイジ ション・サイクルと変換が連続して行われます(表!!!を参照)。 CONTCが"ハイ"に立ち上がる以前にAOおよびA1レジスタ(ピ ン19およびピン18 の各々)に最終的にロードされたアドレスのい ずれかが、シーケンシャル連続変換モードへの最初のアドレス となります。(例えば、チャンネル1が最初のアドレスとして選択 された場合、次にチャンネル2が続き、それからチャンネル3と いう具合に続きます)。デバイスが連続変換モードにある時、A0 およびA1のアドレス入力は、出力となります。 BUSY が変換の最 後で立ち上がる時、AOおよびA1は、次の変換の始まりでBUSY が"ロー"になる時に変換されるチャンネル・アドレスを出力し ます。データは、BUSYが立ち上がる時に、ひとつ前のチャンネ ルに対して有効になります。連続変換モードにおけるチャンネ ル選択タイミングに関しては、表IVaおよび図7を参照してくだ さい。PWRD(ピン26)はマルチプレクサ・アドレスをゼロにリ セットするために使用することができます。

PWRDを最小200nsの間"ハイ"にすると、ADS7825はパワーダウン・モードになります。PWRDが"ロー"に戻ると、マルチプレクサ・アドレスはゼロにリセットされます。連続変換モードがイネーブルの場合には、最初の変換はチャンネル0で行われ、次の変換は上位のチャンネルを通して行われ、チャンネル3の次はチャンネル0に戻ります。

PWRDが長時間"ハイ"を保持した場合、REF(ピン7)パイパス・コンデンサ(内部リファレンスを使用している場合)、およびCAP(ピン6)パイパス・コンデンサ(内部および外部リファレンスを使用している場合)は放電を起こします。連続変換モードはバイパス・コンデンサが再充電して安定するまで(2.2 μFコンデンサで1msを推奨)イネーブルすることができません。さらに、連続変換モードではPWRDに短いパルスを加えたとしても最小アクイジション時間に適応するまでイネーブルすることができません。

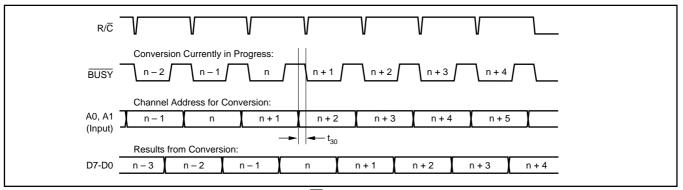

# マニュアルチャンネル選択(CONTC=0V)

ADS7825のチャンネルはAOおよびA1アドレスピン(ピン19および18の各々)を使用してマニュアルで選択できます。マルチプレクサの真理値表に関しては表IVb、チャンネル選択タイミングに関しては図8を参照してください。

# ADS7825タイミングおよびコントロール

| A1 | A0 | データが有効な<br>チャンネル | 変換すべき、<br>または変換中のチャンネル | 動作説明                        |

|----|----|------------------|------------------------|-----------------------------|

| 0  | 0  | AIN <sub>3</sub> | AIN₀                   | アクイジションまたは変換されたチャンネルが、これらの  |

| 0  | 1  | AIN <sub>0</sub> | AIN₁                   | アドレス・ラインに出力されます。前のチャンネルに対して |

| 1  | 0  | AIN₁             | AIN <sub>2</sub>       | データが有効になります。これらのラインはBUSYが立上 |

| 1  | 1  | AIN <sub>2</sub> | AIN₃                   | がる時にアップデートされます。             |

表IVa. A0およびA1出力(CONTC " ハイ " )

| A1 | A0 | BUSYが"ハイ"時に選択される<br>チャンネル | 動作説明                                                                                                        |

|----|----|---------------------------|-------------------------------------------------------------------------------------------------------------|

| 0  | 0  | AIN₀                      | 変換 "n+1"中に変換されるチャンネルは、変換 "n"が開始される時(BUSYが "ロー"になる)にラッチされる。選択された入力は、変換 "n"が終了した直後にアクイジションされる(BUSYが "ハイ"になる)。 |

| 0  | 1  | AIN₁                      |                                                                                                             |

| 1  | 0  | AIN₂                      |                                                                                                             |

| 1  | 1  | AIN₃                      |                                                                                                             |

表IVb. A0およびA1入力(CONTC " ロー ")

図7. 連続変換モードにおけるチャンネル・アドレス(CONTC " ハイ " 、 CSおよびR/C " ロー ")

図8. 通常の変換モードでのチャンネル・アドレス(CONTCおよびCS " ロー ")

## キャリプレーション

ADS7825は個々のバイポーラ・ゼロ誤差、または個々のチャンネル用のフルスケール誤差を補正する内部機能は備えていません。その代わり、各チャンネルのバイポーラ・ゼロ誤差は±10V入カレンジにおいて16ビット変換器としては最小限のレベルを保証しています(±32LSBs)。加えて、チャンネル誤差は互いに16LSB以内にマッチングしています。

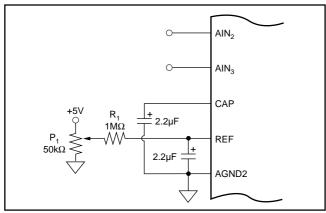

フルスケール誤差に関しては、図9の回路が使用可能です。これはいかなるシングル・チャンネル用のフルスケール誤差もゼロにセットされるようにリファレンスを調整することができます。また、チャンネルの間のマッチングにより、他のチャンネルのフルスケール誤差は小さな値になります。

図9. フルスケール・トリム

# リファレンス

ADS7825は、内部の2.5Vのリファレンスまたは外部リファレンスで動作することができます。ピン7に外部リファレンスを与えることによって内部リファレンスをバイパスすることができます。

#### **REF**

REF(ピン7)は、外部リファレンスの入力または2.5Vの内部リファレンスの出力です。2.2µFのタンタル・コンデンサをグランドからREFピンのできる限り近くに接続して下さい。このコンデンサとREFの出力抵抗は、リファレンス雑音の帯域幅を制限するローパスフィルタを形成します。これより小さい値のコンデンサを使用すると、多くの雑音を発生しSNRおよびSINADを劣化させます。REFピンで外部ACまたはDC負荷をドライブしないで下さい。

外部リファレンスの範囲は2.3Vから2.7Vで、LSBの実際の大きさを決定します。リファレンス電圧を増大すると、フルスケール範囲とコンパータのLSBが増えSNRを改善することができます。

#### CAP

CAP(ピン6)は内部リファレンス・バッファの出力です。 変換サイクル中のCDACのスイッチング電流を最適化するため、2.2μFのタンタル・コンデンサをできる限りCAPピンの近くとグランド間に配置して下さい。このコンデンサはバッファの出力の補償も行います。1μFよりも小さいコンデンサを使用すると、出力バッファの発振を引き起こしCDACに十分な電荷を供給できなくなる可能性があります。また2.2μFよりも大きな値のコンデンサを使用しても性能の目立った改善はされません。

バッファの出力は、1mAまでの電流をDC負荷にドライブすることができます。外部バッファを使用すると、より大きなDC負荷およびAC負荷での内部リファレンスの使用が可能になります。コンバータの性能を劣化させるので、CAPの出力電圧で直接AC負荷をドライブしないで下さい。

#### **PWRD**

PWRD(ピン26)が"八イ"の場合は、リファレンスを含んだすべてのアナログ回路がパワーダウンされます。前の変換データは内部レジスタに記憶されるため読み取り可能です。PWRDが"八イ"の場合は変換コマンドは無意味なデータを発生します。PWRDを"ロー"に戻す時にはREF(ピン7)およびCAP(ピン6)のコンデンサが再充電するために十分な時間を必要とします。2.2μFコンデンサに対しては変換結果が有効となる前に、少なくとも1msの再充電またはセトリング時間が必要になります。

# レイアウト

## 電源

最高の性能を得るためには、アナログおよびデジタル電源ピンを同一の+5V電源に接続し、またアナログとデジタル・グランドを接続して下さい。電気的仕様の部分で示されているようにADS7825は90%の電力をアナログ回路に使用しますので、ADS7825はアナログコンポーネントとして考えて下さい。

A/Dのための+5Vの電力は、システムのデジタル・ロジックに使用される+5Vから分離して下さい。 $V_{s1}$ および $V_{s2}$ (ピン28、27)をデジタル電源に直接接続すると、デジタル・ロジックからのスイッチング雑音によってコンパータの性能が落ちてしまいます。最高の性能を得るためには、+5V電源は他のアナログ・シグナル・コンディショニングなどに使用されているアナログ電源を使用して下さい。+12Vまたは+15Vの電源がある場合は、簡素な+5Vのレギュレータを使用することができます。もしもデジタル電源でコンパータに電源供給しなければならない場合(どうしても必要な場合に限る)は、電源を正しくフィルタして下さい。フィルタされたデジタル電源を使用する場合もレギュレートされたアナログ電源を使用する場合も、 $V_{s1}$ と $V_{s2}$ の両方を同一の+5Vソースに接続して下さい。

## グランディング

ADS7825には3つのグランドピンがあります。DGNDはデジタル電源グランド、AGND2はアナログ電源グランドです。また、AGND1はA/Dのすべての内部のアナログ信号の基準となるグランドです。AGND1は電流に誘導された電圧印可に対してより敏感なので、電源へのリターンパスの抵抗は最小にしておいて下さい。

A/Dのすべてのグランド・ピンはシステムのデジタル・ロジック・グランドから分離されたアナログ・グランド・プレーンに接続して下さい。アナログおよびデジタル・グランド・プレーンはどちらも、できる限り電源の近くでシステムにグランドして下さい。こうすると、電源グランドへの同相インピーダンスを通してアナログ・グランドの変調を引き起こすダイナミック・デジタル・グランド電流を防ぐのに役立ちます。

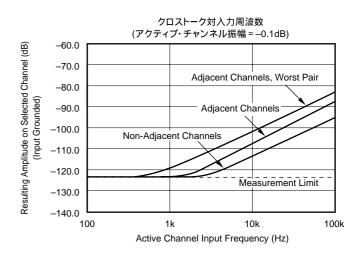

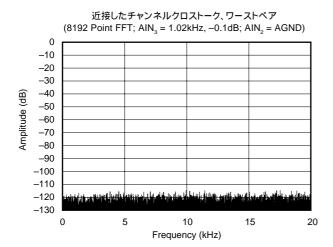

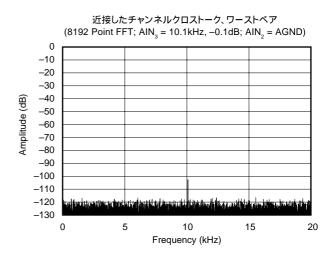

### クロストーク

チャンネル間クロストークのワーストケース対入力周波数を代表的性能曲線に示します。1kHz入力信号フルスケールを使用した場合、ADS7825のクロストークのワーストケースは-115dBよりも良い値となり、これは多くのアプリケーションに適していますが、クロストークが問題となる場合は次のことに注意して下さい。クロストークのワーストケースは通常、チャンネル3から2においてです。特にチャンネル3から他のチャンネルへのクロストークは、他のチャンネルからチャンネル3へのものよりも悪くなります。これは、チャンネル3が他のチャンネルよりもADS7825のリファレンスに近接しているためです。これは、チャンネル間およびチャンネル3からリファレンスへの2つのカップリングモードを引き起こします。一般的には、クロストークが問題となる時は、チャンネル3に高い周波数の信号を設定することは避けて下さい。

ワーストケースのクロストークは、クロストーク対入力周波数の性能曲線に示すとおり、チャンネル3からチャンネル2の間で起こります。その他の近接したチャンネルは、近接していないチャンネルが通常10dB以上良好なのに対し、数dB良い値になります。もし特定のチャンネルをクロストークからできるだけ離さなければならない場合は、チャンネル0が最も適しており、そしてチャンネル1は最も低い周波数の信号に使用します。もし2つの信号のクロストークをできるだけ小さくしたい場合は、チャンネル0および2を低い周波数に設定し、他のチャンネルに低感度な入力を設定します。

すべてのチャンネルにおいてクロストークが問題となる場合は、代表的性能曲線に示されているクロストークのグラフが、どれか2つのチャンネルの間のものであるということを忘れないで下さい。与えられたチャンネルの総クロストークは他のチャンネルすべてからのクロストークの合計です。隣接しないチャンネル間のクロストークは非常に小さいため、これらの影響は非常に小さくなります。代表的性能曲線に示すクロストーク対入力周波数のグラフに6dB加算した値が、ワーストケース・クロストークの絶対値を得るための良い近似となります。

# シグナル・コンディショニング

多くのCMOS A/Dコンパータのサンプル/ホールドに使用されるFETスイッチは、かなりの量のチャージ・インジェクションを放出し、ドライブしているオペアンプを発振させる可能性があります。ADS7825のサンプリングFETスイッチによるチャージ・インジェクションの量は、電荷再分配DAC(CDAC)方式を採用した類似のADSの約5から10%です。またADS7825は、放出された電荷の振幅を減衰させる抵抗性のフロント・エンドを備えており、その結果、A/Dの前段のシグナル・コンディショナをドライブ可能なオペアンプであれば、ADS7825をドライブすることができます。

ADS7825の抵抗性フロント・エンドは、±15Vまでの過電圧への保護を保証します。この保護機能により多くの場合外部の過電 圧保護回路は不用になります。

#### 中間ラッチ

ADS7825にはパラレル・ポート用のトライステート出力がありますが、変換中にバスがアクティブになる場合は中間ラッチを使用して下さい。また変換中にバスがアクティブにならなければ、トライステート出力はA/Dを同じバス上の他の周辺装置から分離するのに使うことができます。

中間ラッチは、すべてのモノリシックA/Dコンパータに有効です。ADS7825の内部LSBサイズは38μVです。パラレル・ポートの高速スイッチング信号からのトランジェントは、A/Dがトライステートの時でもサブストレートを通してアナログ回路と結合することがあり、コンパータの性能を劣化する可能性があります。

ADS7825を正しいレイアウト、グランディングおよびバイパスで使用すれば誤差の影響を数LSBに抑えることができます。いくつかのケースでは、この誤差がコンバータの雑音の増大としてとらえられ、単純に平均化することにより除去されます。他では、誤差は不規則ではなく、平均化しても変換結果に誤差を与えます。劣悪なグランディング、バイパス、および高速のデジタル信号は数10LSBにも達する重大な誤差を引き起こします。

# 外観

17

©BBJ980403K