# ADS7811

# 16-Bit 250kHz Sampling CMOS ANALOG-to-DIGITAL CONVERTER

### FEATURES

- 250kHz SAMPLING RATE

- COMPLETE WITH S/H, REF, CLOCK, ETC.

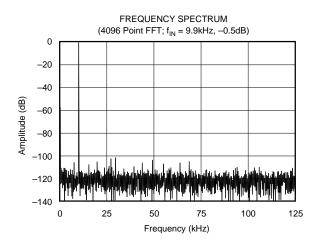

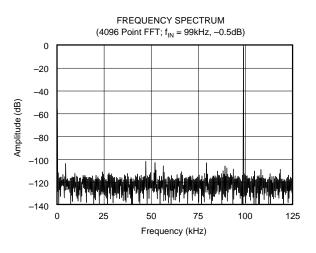

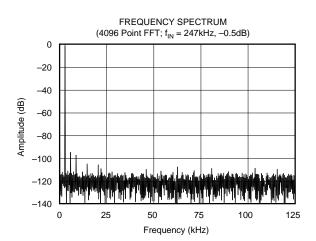

- 96dB min SFDR WITH 100kHz INPUT

- 84dB min SINAD

- ±2.5V INPUT RANGE

- 28-LEAD SOIC

### **APPLICATIONS**

- WIRELESS BASE STATIONS

- SPECTRUM ANALYSIS

- IMAGING SYSTEMS

- DATA ACQUISITION

## DESCRIPTION

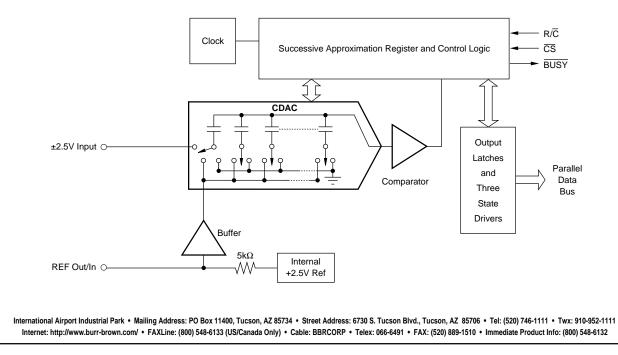

The ADS7811 is a complete 16-bit sampling analogto-digital (A/D) converter featuring excellent AC performance and a 250kHz throughput rate. The design includes a 16-bit capacitor-based SAR A/D converter with an inherent sample and hold (S/H), a precision reference, and an internal clock. Spuriousfree dynamic range with a 100kHz full-scale sinewave input is typically greater than 100dB. The ±2.5V input range allows development of precision systems using only ±5V supplies. The converter is available in a 28-lead SOIC package specified for operation over the industrial  $-25^{\circ}$ C to  $+85^{\circ}$ C temperature range.

## **SPECIFICATIONS**

At  $T_A = -25^{\circ}C$  to +85°C,  $f_S = 250$ kHz, +V<sub>S</sub> = +5V, and -V<sub>S</sub> = -5V, using internal reference, unless otherwise specified.

|                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                        | ADS7811U       |                                                        |                                             |                                                                                        |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------------------------------------------------|---------------------------------------------|----------------------------------------------------------------------------------------|

| PARAMETER                                                                                                                                                                                                                                                           | CONDITIONS                                                                                                                                                                                             | MIN            | TYP                                                    | МАХ                                         | UNITS                                                                                  |

| RESOLUTION                                                                                                                                                                                                                                                          |                                                                                                                                                                                                        |                |                                                        | 16                                          | Bits                                                                                   |

| ANALOG INPUT<br>Voltage Range<br>Impedance<br>Capacitance                                                                                                                                                                                                           | After Input Capacitor is Charged                                                                                                                                                                       |                | ±2.5V<br>100<br>30                                     |                                             | V<br>MΩ<br>pF                                                                          |

| THROUGHPUT SPEED<br>Conversion Cycle<br>Throughput Rate                                                                                                                                                                                                             | Acquire and Convert                                                                                                                                                                                    | 250            |                                                        | 4.0                                         | μs<br>kHz                                                                              |

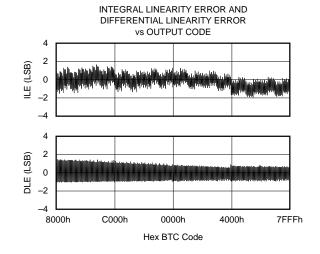

| DC ACCURACY<br>Integral Linearity Error<br>No Missing Codes<br>Transition Noise <sup>(2)</sup><br>Full Scale Error <sup>(3)</sup><br>Full Scale Error Drift<br>Full Scale Error Drift<br>Bipolar Zero Error<br>Bipolar Zero Error Drift<br>Power Supply Sensitivity | External 2.5000V Reference<br>External 2.5000V Reference<br>+V <sub>S</sub> ±5%, -V <sub>S</sub> ±5%                                                                                                   | 15             | 0.8<br>$\pm 7$<br>$\pm 0.2$<br>2<br>$\pm 2$<br>$\pm 6$ | ±4<br>±0.5<br>±10<br>±16                    | LSB <sup>(1)</sup><br>Bits<br>LSB<br>%<br>ppm/°C<br>%<br>ppm/°C<br>mV<br>ppm/°C<br>LSB |

| AC ACCURACY<br>Spurious-Free Dynamic Range<br>Total Harmonic Distortion<br>Signal-to-(Noise+Distortion)<br>Signal-to-Noise<br>Usable Bandwidth <sup>(5)</sup><br>Aperture Delay                                                                                     | $\label{eq:fin} \begin{array}{l} f_{\rm IN} = 100 \text{kHz} \\ f_{\rm IN} = 100 \text{kHz} \\ f_{\rm IN} = 100 \text{kHz} \\ -60 \text{dB} \ \text{Input} \\ f_{\rm IN} = 100 \text{kHz} \end{array}$ | 96<br>84<br>84 | 100<br>-98<br>87<br>28<br>87<br>1<br>40                | -96                                         | dB <sup>(4)</sup><br>dB<br>dB<br>dB<br>dB<br>MHz<br>ns                                 |

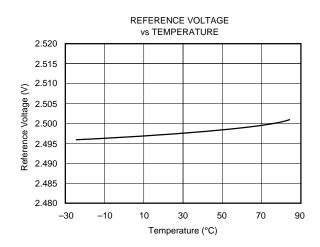

| REFERENCE<br>Internal Reference Voltage<br>Internal Reference Source Current<br>Internal Reference Drift<br>External Reference Voltage Range<br>External Reference Current Drain                                                                                    | V <sub>REF</sub> = +2.5V                                                                                                                                                                               | 2.48           | 2.5<br>1<br>15<br>2.5                                  | 2.52                                        | V<br>μA<br>ppm/°C<br>V<br>μA                                                           |

| DIGITAL INPUTS<br>Logic Levels<br>V <sub>IL</sub><br>V <sub>IH</sub><br>I <sub>IL</sub><br>I <sub>IH</sub>                                                                                                                                                          |                                                                                                                                                                                                        | -0.3<br>+2.8   |                                                        | +0.8<br>+V <sub>S</sub> +0.3V<br>±10<br>±10 | V<br>V<br>μΑ<br>μΑ                                                                     |

| DIGITAL OUTPUTS<br>Data Format<br>Data Coding<br>V <sub>OL</sub><br>V <sub>OH</sub><br>Leakage Current<br>Output Capacitance                                                                                                                                        | $I_{SINK} = 1.6mA$<br>$I_{SOURCE} = 200\mu A$<br>High-Z State,<br>$V_{OUT} = 0V$ to $V_{DIG}$<br>High-Z State                                                                                          | Bi<br>+4       | Parallel 16 bits<br>nary Two's Compleme                | nt<br>+0.4<br>±5<br>15                      | ν<br>ν<br>μΑ<br>pF                                                                     |

| DIGITAL TIMING<br>Bus Access Time<br>Bus Relinquish Time                                                                                                                                                                                                            |                                                                                                                                                                                                        |                |                                                        | 83<br>83                                    | ns                                                                                     |

| POWER SUPPLIES<br>+V <sub>S</sub><br>-V <sub>S</sub><br>+I <sub>S</sub><br>-I <sub>S</sub><br>Power Dissipation                                                                                                                                                     |                                                                                                                                                                                                        | +4.75<br>-5.25 | +5<br>-5<br>+30<br>-10<br>200                          | +5.25<br>-4.75<br>250                       | V<br>V<br>mA<br>mA<br>mW                                                               |

| TEMPERATURE RANGE<br>Specified Performance<br>Storage                                                                                                                                                                                                               |                                                                                                                                                                                                        | -25<br>-55     |                                                        | +85<br>+125                                 | °C<br>℃                                                                                |

NOTES: (1) LSB means Least Significant Bit. For the 16-bit,  $\pm 2.5V$  input ADS7811, one LSB is 76 $\mu$ V. (2) Typical rms noise at worst case transitions and temperatures. (3) Full scale error is the worst case of –Full Scale or +Full Scale untrimmed deviation from ideal first and last code transitions, divided by the transition voltage (not divided by the full-scale range) and includes the effect of offset error. (4) All specifications in dB are referred to a full-scale  $\pm 2.5V$  input. (5) Usable Bandwidth defined as Full-Scale input frequency at which Signal-to-(Noise+Distortion) degrades to 60dB, or 10 bits of accuracy.

#### **ABSOLUTE MAXIMUM RATINGS**

| +V <sub>S</sub>                   |                                 |

|-----------------------------------|---------------------------------|

| –V <sub>S</sub>                   |                                 |

| Digital Inputs                    | –0.3V to +V <sub>S</sub> + 0.3V |

| Maximum Junction Temperature      |                                 |

| Internal Power Dissipation        |                                 |

| Lead Temperature (soldering, 10s) | +300°C                          |

## ELECTROSTATIC DISCHARGE SENSITIVITY

This integrated circuit can be damaged by ESD. Burr-Brown recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

ESD damage can range from subtle performance degradation to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.

#### PACKAGE/ORDERING INFORMATION

| PRODUCT  | PACKAGE     | PACKAGE<br>DRAWING<br>NUMBER <sup>(1)</sup> | TEMPERATURE<br>RANGE |  |

|----------|-------------|---------------------------------------------|----------------------|--|

| ADS7811U | 28-Pin SOIC | 217                                         | –25°C to +85°C       |  |

NOTE: (1) For detailed drawing and dimension table, please see end of data sheet, or Appendix C of Burr-Brown IC Data Book.

The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user's own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.

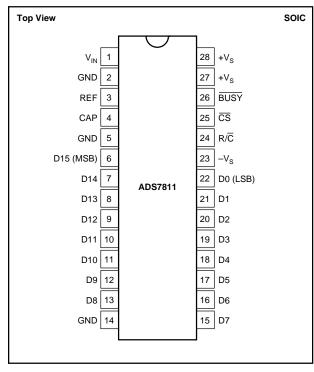

| PIN # | NAME            | DESCRIPTION                                                                                                                                                                                                                                                                                                       |

|-------|-----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | V <sub>IN</sub> | Analog Input. Full-scale input range is ±2.5V.                                                                                                                                                                                                                                                                    |

| 2     | GND             | Ground.                                                                                                                                                                                                                                                                                                           |

| 3     | REF             | Reference Input/Output. Outputs internal reference of +2.5V nominal. Can also be driven by external system reference. In both cases, connect to ground with a 0.1µF ceramic capacitor in parallel with 2.2µF tantalum capacitor.                                                                                  |

| 4     | CAP             | Reference compensation capacitor. Use a parallel combination of a 0.1µF ceramic capacitor and a 2.2µF tantalum capacitor.                                                                                                                                                                                         |

| 5     | GND             | Ground.                                                                                                                                                                                                                                                                                                           |

| 6     | D15 (MSB)       | Data Bit 15. Most Significant Bit (MSB) of conversion results. Hi-Z state when $\overline{CS}$ is HIGH, when $R/\overline{C}$ is LOW or when a conversion is in progress.                                                                                                                                         |

| 7     | D14             | Data Bit 14. Hi-Z state when $\overline{CS}$ is HIGH, when $R/\overline{C}$ is LOW or when a conversion is in progress.                                                                                                                                                                                           |

| 8     | D13             | Data Bit 13. Hi-Z state when $\overline{CS}$ is HIGH, when $R/\overline{C}$ is LOW or when a conversion is in progress.                                                                                                                                                                                           |

| 9     | D12             | Data Bit 12. Hi-Z state when $\overline{CS}$ is HIGH, when $R/\overline{C}$ is LOW or when a conversion is in progress.                                                                                                                                                                                           |

| 10    | D11             | Data Bit 11. Hi-Z state when $\overline{CS}$ is HIGH, when $R/\overline{C}$ is LOW or when a conversion is in progress.                                                                                                                                                                                           |

| 11    | D10             | Data Bit 10. Hi-Z state when $\overline{CS}$ is HIGH, when $\overline{R/C}$ is LOW or when a conversion is in progress.                                                                                                                                                                                           |

| 12    | D9              | Data Bit 9. Hi-Z state when $\overline{CS}$ is HIGH, when $R/\overline{C}$ is LOW or when a conversion is in progress.                                                                                                                                                                                            |

| 13    | D8              | Data Bit 8. Hi-Z state when $\overline{CS}$ is HIGH, when $R/\overline{C}$ is LOW or when a conversion is in progress.                                                                                                                                                                                            |

| 14    | GND             | Ground.                                                                                                                                                                                                                                                                                                           |

| 15    | D7              | Data Bit 7. Hi-Z state when $\overline{CS}$ is HIGH, when $R/\overline{C}$ is LOW or when a conversion is in progress.                                                                                                                                                                                            |

| 16    | D6              | Data Bit 6. Hi-Z state when $\overline{CS}$ is HIGH, when $R/\overline{C}$ is LOW or when a conversion is in progress.                                                                                                                                                                                            |

| 17    | D5              | Data Bit 5. Hi-Z state when $\overline{CS}$ is HIGH, when $R/\overline{C}$ is LOW or when a conversion is in progress.                                                                                                                                                                                            |

| 18    | D4              | Data Bit 4. Hi-Z state when $\overline{CS}$ is HIGH, when $R/\overline{C}$ is LOW or when a conversion is in progress.                                                                                                                                                                                            |

| 19    | D3              | Data Bit 3. Hi-Z state when $\overline{CS}$ is HIGH, when $R/\overline{C}$ is LOW or when a conversion is in progress.                                                                                                                                                                                            |

| 20    | D2              | Data Bit 2. Hi-Z state when $\overline{CS}$ is HIGH, when $R/\overline{C}$ is LOW or when a conversion is in progress.                                                                                                                                                                                            |

| 21    | D1              | Data Bit 1. Hi-Z state when $\overline{CS}$ is HIGH, when $R/\overline{C}$ is LOW or when a conversion is in progress.                                                                                                                                                                                            |

| 22    | D0 (LSB)        | Data Bit 0. Least Significant Bit (LSB) of conversion results. Hi-Z state when $\overline{CS}$ is HIGH, when $R/\overline{C}$ is LOW or when a conversion is in progress.                                                                                                                                         |

| 23    | -V <sub>S</sub> | Negative supply input. Nominally -5V. Decouple to analog ground with 0.1µF ceramic and 10µF tantalum capacitors.                                                                                                                                                                                                  |

| 24    | R/Ē             | Read/convert input. With R/C HIGH, CS going LOW will enable the output data bits if a conversion is not in progress. With R/C LOW, CS going LOW will start a conversion if one is not already in progress.                                                                                                        |

| 25    | CS              |                                                                                                                                                                                                                                                                                                                   |

| 25    | CS              | Chip select. With R/C LOW, CS going LOW will initiate a conversion if one is not already in progress. With R/C HIGH, CS                                                                                                                                                                                           |

|       | BUSY            | going LOW will enable the output data bits if a conversion is not in progress.                                                                                                                                                                                                                                    |

| 26    | BOSY            | Busy output. Falls when a conversion is started, and remains LOW until the conversion is completed. With $\overline{CS}$ LOW and R/ $\overline{C}$ HIGH, output data will be valid when $\overline{BUSY}$ rises, so that the rising edge can be used to latch the data. $\overline{CS}$ or R/ $\overline{C}$ must |

|       |                 | be HIGH within 250ns after BUSY rises or another conversion will start without time for signal acquisition.                                                                                                                                                                                                       |

| 27    | +V <sub>S</sub> | Positive supply input. Nominally +5V. Connect directly to pin 28.                                                                                                                                                                                                                                                 |

| 28    | +V <sub>S</sub> | Positive supply input. Nominally +5V. Connect directly to pin 27. Decouple to ground with 0.1µF ceramic and 10µF tantalum capacitors.                                                                                                                                                                             |

TABLE I. Pin Assignments.

### **PIN CONFIGURATION**

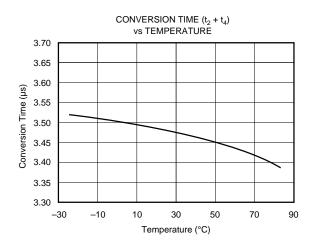

## **TYPICAL PERFORMANCE CURVES**

At  $T_A = -25^{\circ}C$  to +85°C,  $f_S = 250$ kHz, +V<sub>S</sub> = +5V, and -V<sub>S</sub> = -5V, using internal reference, unless otherwise specified.

ADS7811

## **BASIC OPERATION**

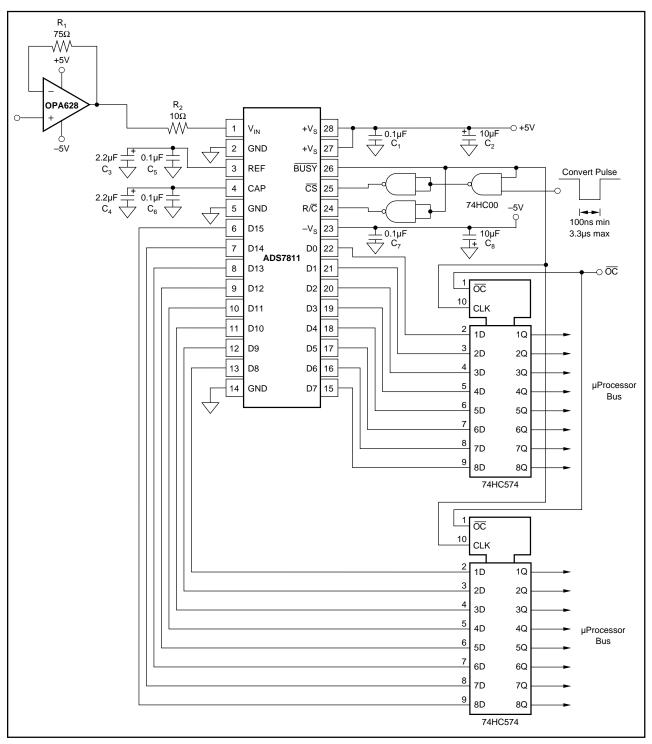

Figure 1 shows the recommended circuit for operation of the ADS7811. A falling edge on the convert pulse signal places the sample and hold into the hold mode and initiates a conversion. When the conversion is complete, the pins D15 through D0 become active and the result of the conversion

is placed on these outputs. In the circuit shown in Figure 1, the rising edge of  $\overline{\text{BUSY}}$  latches the result into the 74HC574s.

After the conversion is complete, the ADS7811 sample and hold returns to the sample mode and begins acquiring the input signal for the next conversion. Allowing  $4\mu$ s between falling edges of the convert pulse signal assures adequate acquisition time for the internal sample and hold.

FIGURE 1. Basic Operation.

6

### TIMING

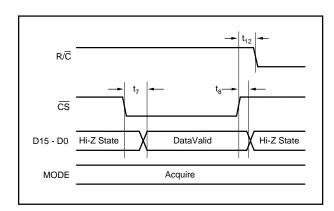

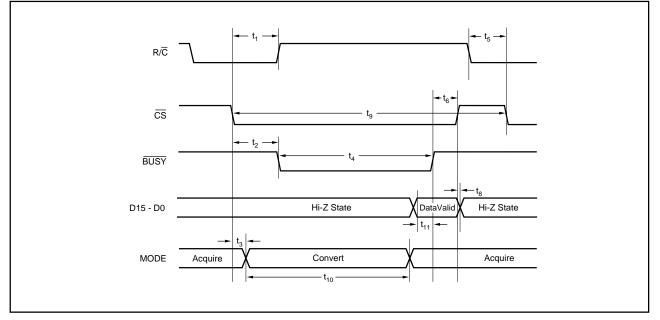

The timing shown in Figure 2 and Table II is the recommended method of operating the ADS7811. The falling edge of  $\overline{CS}$  initiates the conversion. During the conversion, the digital outputs are tri-stated and  $\overline{BUSY}$  is LOW. Near the end of the conversion, the digital outputs become active with the most recent conversion result. After a brief delay (see time t<sub>11</sub> in Figure 2 and Table II),  $\overline{BUSY}$  rises. The rising edge of  $\overline{BUSY}$  is used to latch the digital result in Figure 1.

### $R/\overline{C}$ and $\overline{CS}$

The  $R/\overline{C}$  (read/convert) and  $\overline{CS}$  signals control the start of conversion and, when a conversion is not in progress, the status of the digital outputs D15 through D0. It is possible to start a conversion by taking  $\overline{CS}$  LOW and then taking  $R/\overline{C}$  LOW. However, this is not recommended and will result in a significant decrease in signal-to-noise ratio. This is due to

| SYMBOL          | DESCRIPTION                                                    | MIN            | TYP | MAX | UNITS |

|-----------------|----------------------------------------------------------------|----------------|-----|-----|-------|

| t <sub>1</sub>  | $\overline{\text{CS}}$ to $\text{R}/\overline{\text{C}}$ Delay | t <sub>2</sub> |     | 200 | ns    |

| t <sub>2</sub>  | CS to BUSY Delay                                               |                | 40  |     | ns    |

| t <sub>3</sub>  | Aperture Delay                                                 |                | 40  |     | ns    |

| t <sub>4</sub>  | BUSY LOW                                                       |                | 3.5 |     | μs    |

| t <sub>5</sub>  | $R/\overline{C}$ LOW to $\overline{CS}$ LOW                    | 100            |     |     | ns    |

| t <sub>6</sub>  | BUSY HIGH to CS HIGH                                           |                |     | 250 | ns    |

| t <sub>7</sub>  | Bus Access Time                                                |                | 10  | 83  | ns    |

| t <sub>8</sub>  | Bus Relinquish Time                                            |                |     | 83  | ns    |

| t <sub>9</sub>  | Throughput Time                                                |                |     | 4   | μs    |

| t <sub>10</sub> | Conversion Time                                                |                | 3.4 |     | μs    |

| t <sub>11</sub> | Data Valid to BUSY HIGH                                        | 25             | 35  |     | ns    |

| t <sub>12</sub> | $\overline{\text{CS}}$ to R/ $\overline{\text{C}}$ Setup Time  | 40             |     |     | ns    |

TABLE II. Conversion Timing.

the digital outputs tri-stating while the sample and hold transitions to the hold mode. The change in digital outputs results in noise being coupled onto the hold capacitor.

If a conversion is not in progress or is just about to finish, the digital outputs will be active when  $R/\overline{C}$  is HIGH and  $\overline{CS}$  is LOW. This is shown in Figure 2 and Figure 3. It is possible to return  $\overline{CS}$  HIGH during the initial part of the conversion (as is done with  $R/\overline{C}$ ) and prevent the digital outputs from becoming active. At a later time, the digital results could be read by taking  $\overline{CS}$  LOW. It is also possible to leave  $R/\overline{C}$  LOW, take  $\overline{CS}$  HIGH during the conversion, and read the results at a later time by taking  $R/\overline{C}$  HIGH and  $\overline{CS}$  LOW.

Following a conversion, if  $R/\overline{C}$  and  $\overline{CS}$  are both LOW 250ns after  $\overline{BUSY}$  rises, then a new conversion will be initiated without allowing the proper acquisition period for the sample and hold.  $R/\overline{C}$  must remain HIGH or  $\overline{CS}$  must be taken HIGH within 250ns of  $\overline{BUSY}$  rising.

$R/\overline{C}$  and  $\overline{CS}$  should remain static prior to that start of conversion and during the later part of a conversion. To start

FIGURE 3. Bus Timing.

FIGURE 2. ADS7811 Timing.

a conversion,  $R/\overline{C}$  should be taken LOW at least 100ns before  $\overline{CS}$  is taken LOW.  $R/\overline{C}$  and/or  $\overline{CS}$  should be taken HIGH during the early part of the conversion, preferably within 200ns of the start of the conversion. If these times are not observed, then there is risk that the transition of these digital signals may affect the conversion result.

The three NAND gates shown in Figure 1 can be used to generate  $R/\overline{C}$  and  $\overline{CS}$  signals from a single negative going pulse. The pulse must not be longer than 3.3µs or a second conversion may be initiated immediately after the first.

### BUSY

$\overline{\text{BUSY}}$  goes LOW when a conversion is started and remains LOW throughout the conversion. Just prior to  $\overline{\text{BUSY}}$  going HIGH, the digital outputs become active with the conversion result. Time t<sub>11</sub>, shown in Figure 2, should provide adequate time for the ADS7811 to drive the digital outputs to a valid logic state before  $\overline{\text{BUSY}}$  rises. As shown in Figure 1 and 2, the rising edge of  $\overline{\text{BUSY}}$  can be used to latch the digital result into an external component.

### DIGITAL OUTPUT

The ADS7811's digital output is in Binary Two's Complement (BTC) format. Table III shows the relationship between the digital output word and analog input voltage under ideal conditions.

|                                |           | DIGITAL OUTPUT          |          |  |

|--------------------------------|-----------|-------------------------|----------|--|

|                                | ANALOG    | BINARY TWO'S COMPLEMENT |          |  |

| DESCRIPTION                    | INPUT     | BINARY CODE             | HEX CODE |  |

| Full Scale Range               | ±2.5V     |                         |          |  |

| Least Significant<br>Bit (LSB) | 76μV      |                         |          |  |

| +Full Scale<br>(2.5V – 1LSB)   | 2.499924V | 0111 1111 1111 1111     | 7FFF     |  |

| Midscale                       | 0V        | 0000 0000 0000 0000     | 0000     |  |

| One LSB below<br>Midscale      | -76μV     | 1111 1111 1111 1111     | FFFF     |  |

| -Full Scale                    | –2.5V     | 1000 0000 0000 0000     | 8000     |  |

Table III. Ideal Input Voltages and Output Codes.

### REFERENCE

The ADS7811 can be operated with the internal 2.5V reference or an external reference. By applying an external reference to the REF pin, the internal reference is bypassed. The reference voltage at REF is buffered internally.

The voltage at the reference input sets the full-scale range of the converter. With the internal 2.5V reference, the input range is  $\pm 2.5$ V. Thus, the input range of the converter's analog input is simply  $\pm V_{REF}$ , where  $V_{REF}$  is the voltage at the reference input. Because of internal gain and offset error, the input range will not be exactly  $\pm V_{REF}$ . The full-scale error of the converter with an external reference will typically be 0.25% or less. The bipolar zero error will be similar to that listed in the Specifications Table. The range for the external reference is 2.3V to 2.7V. While the ADS7811 will operate using an external reference, the specifications are only guaranteed when the internal reference is used.

#### **REF PIN**

The REF pin itself should be bypassed with a  $0.1\mu$ F ceramic capacitor in parallel with a  $2.2\mu$ F tantalum capacitor. While both capacitors should be physically close to the ADS7811, it is very important that the ceramic capacitor be placed as close as possible.

The REF voltage should not be used to drive a large load or any load which is dynamic. A large load will reduce the reference voltage and the corresponding input range of the converter. A dynamic load will modulate the reference voltage and this modulation will be present in the converter's output data.

#### CAP PIN

The voltage on the CAP pin is the output of the reference buffer. This pin should be bypassed with a  $0.1\mu$ F ceramic capacitor in parallel with a  $2.2\mu$ F tantalum capacitor. While both capacitors should be physically close to the ADS7811, it is very important that the ceramic capacitor be placed as close as possible.

The CAP pin connects to the internal reference buffer and directly to the binary weighted capacitor array of the converter. Thus, the signal at the CAP pin has high-frequency glitches which occur at each bit decision. For this reason, the CAP voltage should not be used to provide a reference voltage for external circuitry.

### LAYOUT

The layout of the ADS7811 and accompanying components will be critical for optimum performance. Use of an analog ground plane is essential. Use of +5V and -5V power planes is not critical as long as the supplies are well bypassed, and the traces connecting +5V and -5V to the power connector are not too long or too thin.

The two  $+V_s$  power pins of the ADS7811 must be tied together. The voltage source for these pins should also power the input buffer and the 74HC00 shown in Figure 1. This supply should separate from the positive +5V supply for the system's digital logic

Three ground pins are present on the ADS7811: pin 2, pin 5, and pin 14. These should all be tied to the analog ground plane. The analog ground plane should extend underneath all analog signal conditioning components and up to the 74HC574s (or equivalent components) shown in Figure 1. The 74HC574s should not be located more than several inches from the ADS7811.

The ground for the 74HC574s should be connected to the digital ground. The analog ground plane should extend up to

the 74HC574s but should be kept at least 1/4" (6mm) distant from the digital ground plane (if present). The analog and digital grounds planes should not overlap at any point.

#### INTERMEDIATE LATCHES

The 74HC574s shown in Figure 1 isolate the ADS7811 from digital signals on a microprocessor, digital signal processor (DSP), or microcontroller bus. This is necessary because of the precision needed within the ADS7811. The weight of a single LSB in the ADS7811 is 76 $\mu$ V, and the comparator must be able to resolve differences in voltage to this level. External digital signals which transition during the conversion can easily couple onto the substrate and produce voltages larger than this.

In place of the 74HC574s, it might be possible to use a FIFO or similar type of memory device. For many systems, it may be difficult to go directly from the ADS7811 into a microcontroller or DSP even if the ADS7811 is not connected to shared bus. The reason for this is that the outputs are active only during the acquisition period.

#### SIGNAL CONDITIONING

The ADS7811 input essentially consists of a switch and a capacitor. In the acquisition or sample mode, the switch is closed and the input signal drives the capacitor directly. When a conversion is started, the switch is opened capturing the input signal at that moment. This voltage is held on the capacitor for the remainder of the conversion.

While this provides for a wide bandwidth sample and hold function and results in excellent AC performance, this architecture requires a high bandwidth, precision op amp to drive the analog input. The op amp and configuration shown in Figure 1 is highly recommended. The amplifier should be placed within 1 to 2 inches (25 to 50mm) of the ADS7811, and the layout guidelines in the OPA628 data sheet should be strictly followed.