# 12**ビット**10μs**シリアル**CMOSサンプリング A/D**コンバータ**

### 特長

サンプリング・レート: 100kHzSINAD: 45kHz入力で72dB

積分直線性誤差および微分直線性誤差: ± 1/2 LSB

● 6つの入力レンジ

● シリアル出力

◆ +5∨単一電源動作

● 16ピットのADS7809とピン・コンパチブル

● 内部または外部のリファレンスを使用可能

● 消費電力: 100mW(最大)

● 20ピン0.3インチ幅プラスチックDIPおよびSOP

● 単純なDSPインターフェース

### 概要

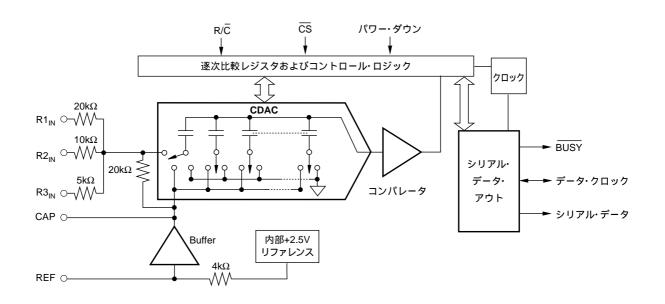

ADS7808は、最新のCMOS構造を使用した完全な12ビット・サンプリングA/Dコンバータです。このコンバータはキャパシタ・ベースの逐次比較型12ビットA/Dコンバータで、S/H、リファレンス、クロック、およびシリアル・データ・インターフェースを内蔵しています。データは内部クロックを使用して出力するか、外部データ・クロックに同期させることができます。ADS7808は、標準DSPプロセッサと組み合わせた場合に使いやすいように、出力同期パルスも供給します。

ADS7808の仕様は100kHzのサンプリング・レートで規定されており、全温度範囲で保証されています。斬新な設計により、+5V単一電源で100mW以下の消費電力で動作し、レーザ・トリムされたスケーリング抵抗により、±10V、0Vから5Vなどさまざまな入力範囲を実現しています。

ADS7808は、20ピンのプラスチック0.3インチ幅DIPおよびSOPで供給され、どちらも-40 から+85 の工業温度範囲で仕様が完全に規定されています。

### 電気的仕様

特に記述がない限り、 $T_A=-40$  から+85 、 $f_S=100$ kHz、 $V_{DIG}=V_{ANA}=+5$ V、内部リファレンスおよび図4に示す固定抵抗を使用。

|                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                         |                | ADS7808P/                        | U                                                             | А                   | DS7808PB/  | UB                                    |                                                                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|----------------------------------|---------------------------------------------------------------|---------------------|------------|---------------------------------------|-----------------------------------------------------------------------------|

| パラメータ                                                                                                                                                                                                                                                                                                   | 条件                                                                                                                                                                      | 最小             | 標準                               | 最大                                                            | 最小                  | 標準         | 最大                                    | 単位                                                                          |

| 分解能                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                         |                |                                  | 12                                                            |                     |            | *                                     | Bits                                                                        |

| <b>アナログ入力</b><br>電圧範囲<br>インピーダンス<br>容量                                                                                                                                                                                                                                                                  |                                                                                                                                                                         |                | ±10                              | 0、0から5Vが<br>表I                                                | など(表 I 参)<br>参照<br> | 照)         |                                       | pF                                                                          |

| <b>スループット速度</b><br>変換時間<br>完全サイクル<br>スループット・レート                                                                                                                                                                                                                                                         | アクイジションおよび変換                                                                                                                                                            | 100            | 5.7                              | 8<br>10                                                       | *                   | *          | *                                     | μs<br>μs<br>kHz                                                             |

| DC精度<br>積分直線性誤差<br>(次分直線性誤差<br>ノーミッシンゲ・コード<br>トランジション・ノイズ(2)<br>フルスケール誤差・ドリフト<br>フルスケール誤差 ドリフト<br>フルスケール誤差 ドリフト<br>バイボーラ・ゼロ誤差 ドリフト<br>ユニポーラ・ゼロ誤差 (3)<br>ユニポーラ・ゼロ誤差 (3)<br>ユニポーラ・ゼロ誤差 (4)<br>ユニポーラ・ゼロ誤差 (5)<br>ユニポーラ・ゼロ誤差 (7)<br>ロ復時間<br>電源感度<br>(V <sub>DIG</sub> = V <sub>ANA</sub> = V <sub>D</sub> ) | Ext. 2.5000V Ref<br>Ext. 2.5000V Ref<br>バイポーラ・レンジ<br>バイポーラ・レンジ<br>0V~10Vレンジ<br>0V~4Vレンジ<br>0V~5Vレンジ<br>ユニポーラ・レンジ<br>1µFコンデンサをCAPに接続<br>+4.75V < V <sub>0</sub> < +5.25V |                | 保証<br>0.1<br>±7<br>±2<br>±2<br>1 | ±0.9<br>±0.9<br>±0.5<br>±0.5<br>±10<br>±5<br>±3<br>±3<br>±0.5 |                     | * ±5  * ±2 | ±0.45<br>±0.45<br>±0.25<br>±0.25<br>* | LSB <sup>(1)</sup> LSB  KSB  M  ppm/ MV  ppm/ mV  mV  ppm/ mV  ppm/ mS  LSB |

| AC <b>精度</b><br>スプリアスフリー・ダイナミック・レンジ(SFDR)<br>全高調波歪(THD)<br>信号/雑音+歪)比(SINAD)<br>信号/雑音比(SNR)<br>フルパワー・パンド幅®                                                                                                                                                                                               | $\begin{split} &f_{\text{IN}} = 45 \text{kHz} \\ &f_{\text{IN}} = 45 \text{kHz} \\ &f_{\text{IN}} = 45 \text{kHz} \\ &f_{\text{IN}} = 45 \text{kHz} \end{split}$        | 80<br>70<br>70 | 90<br>-90<br>73<br>73<br>250     | -80                                                           | *<br>72<br>72       | * * * *    | *                                     | dB <sup>(5)</sup><br>dB<br>dB<br>dB<br>kHz                                  |

| サンプリングのダイナミック特性<br>アパーチャ遅延<br>アパーチャ・ジッタ<br>過渡応答<br>過電圧復帰の                                                                                                                                                                                                                                               | FSステップ                                                                                                                                                                  |                | 40<br>AC仕様に適<br>150              | 合<br>  2                                                      |                     | * *        | *                                     | ns<br>ns<br>μs<br>ns                                                        |

| リファレンス<br>内部リファレンス電圧<br>内部リファレンス・ソース電流                                                                                                                                                                                                                                                                  | 無負荷                                                                                                                                                                     | 2.48           | 2.5<br>1                         | 2.52                                                          | *                   | *          | *                                     | V<br>μA                                                                     |

| (外部にパッファを使用してください)<br>直線性仕様を満たす<br>外部リファレンス電圧範囲<br>外部リファレンス電流ドレイン                                                                                                                                                                                                                                       | Ext. 2.5000V Ref                                                                                                                                                        | 2.3            | 2.5                              | 2.7                                                           | *                   | *          | *                                     | V<br>μA                                                                     |

| <b>デジタル入力</b><br>ロジック・レベル<br>V <sub>IL</sub><br>V <sub>IH</sub><br>I <sub>IL</sub><br>I <sub>IH</sub>                                                                                                                                                                                                   | $V_{IL} = 0V$ $V_{IH} = 5V$                                                                                                                                             | -0.3<br>+2.0   |                                  | +0.8<br>V <sub>D</sub> +0.3V<br>±10<br>±10                    | *                   |            | * * *                                 | V<br>V<br>μA<br>μA                                                          |

このデータシートに記載されている情報は、信頼し得るものと考えておりますが、不正確な情報や記載漏れ等に関して弊社は責任を負うものではありません。情報の使用について弊社は責任を負えませんので、各ユーザーの責任において御使用下さい。価格や仕様は予告なしに変更される場合がありますのでご了承下さい。ここに記載されているいかなる回路についても工業所有権その他の権利またはその実施権を付与したり承諾したりするものではありません。弊社は弊社製品を生命維持に関する機器またはシステムに使用することを承認しまたは保証するものではありません。

## 電気的仕様 (続き)

特に記述がない限り、 $T_a=-40$  ~+85、 $f_s=100$ kHz、 $V_{DIG}=V_{ANA}=+5$ V、内部リファレンスおよび図4に示す固定抵抗を使用します。

|                      |                                                          | ,     | ADS7808P/l | J      | AI             | DS7808PB/I | JB  |     |

|----------------------|----------------------------------------------------------|-------|------------|--------|----------------|------------|-----|-----|

| パラメータ                | 条件                                                       | MIN   | TYP        | MAX    | MIN            | TYP        | MAX | 単位  |

| デジタル出力               |                                                          |       |            |        |                |            |     |     |

| データ・フォーマット           |                                                          |       |            | シリアル   | 12ビット          |            |     |     |

| データ・コーティング           |                                                          |       | バイナリ2      | の補数またに | はストレート         | ・バイナリ      |     |     |

| パイプライン遅延             |                                                          |       |            | 果は変換完了 |                |            |     |     |

| データ・クロック             |                                                          |       |            | は外部データ | <b>ア・クロックを</b> | 選択可能       |     |     |

| 内部                   | EXT/INT " □ — "                                          | 2.3   |            |        |                |            | MHz |     |

| (データ送信時のみ出力)         |                                                          |       |            |        |                |            |     |     |

| 外部                   | EXT/INT " ハイ "                                           | 0.1   |            | 10     | *              |            | *   | MHz |

| (連続動作可能)             |                                                          |       |            |        |                |            |     |     |

| V <sub>OL</sub>      | I <sub>SINK</sub> =1.6mA                                 |       |            | +0.4   |                |            | *   | V   |

| V <sub>OH</sub>      | I <sub>source</sub> =500μA                               | +4    |            | _      | *              |            |     | V   |

| リーケージ電流              | High-Z State                                             |       |            | ±5     |                |            | *   | μΑ  |

| <br>  出力容量           | V <sub>OUT</sub> =0V to V <sub>DIG</sub><br>High-Z State |       |            | 15     |                |            | *   | pF  |

| 山川谷里                 | High-Z State                                             |       |            | 15     |                |            |     | рг  |

| 電源                   |                                                          |       |            |        |                |            |     |     |

| 仕様に規定された性能           |                                                          |       |            |        |                |            |     |     |

| $V_{DIG}$            | V <sub>ANA</sub> と同じか、それ以下でなければならない。                     | +4.75 | +5         | +5.25  | *              | *          | *   | V   |

| V <sub>ANA</sub>     | +4.75                                                    | +5    | +5.25      |        | *              | *          | *   | V   |

| I <sub>DIG</sub>     |                                                          | 0.3   |            |        | *              |            |     | mA  |

| I <sub>ANA</sub>     |                                                          | 16    |            |        | *              |            |     | mA  |

| 消費電力: PWRD " ロー "    | $V_{DIG}=V_{ANA}=5V, f_{S}=100kHz$                       |       |            | 100    |                |            | *   | mW  |

| PWRD "ハイ "           |                                                          |       | 50         |        |                | *          |     | μW  |

| 温度範囲                 |                                                          |       |            |        |                |            |     |     |

| 仕様に規定された性能           |                                                          | -40   |            | +85    | *              |            | *   |     |

| ディレーティングした性能         |                                                          | -55   |            | +125   | *              |            | *   |     |

| 保存                   |                                                          | -65   |            | +150   | *              |            | *   |     |

| 熱抵抗( <sub>JA</sub> ) |                                                          |       |            |        |                |            |     |     |

| プラスチックDIP            |                                                          |       | 75         |        |                | *          |     | /W  |

| SOP                  |                                                          |       | 75         |        |                | *          |     | /W  |

注:(1) LSBは最下位ビットを意味します。±10V入力範囲の場合、1 LSBは4.88mVです。 (2) ワーストケースの遷移および温度における標準的なrmsノイズ。 (3) 図 4 に示す固定抵抗で測定されます。外付けポテンショメータでゼロに調整可能です。 (4) バイポーラ入力レンジの場合、フルスケール誤差はトリムされないーフルスケールまたは+フルスケールのワーストケース値と、理想的な最初および最後のコード・トランジションとの偏差を、遷移電圧で除算(フルスケール・レンジで除算しない)した値で、オフセット誤差の影響が含まれます。ユニポーラ入力レンジの場合、フルスケール誤差は最後のコード・トランジションの偏差を遷移電圧で除算した値です。これにもオフセット誤差の影響が含まれます。 (5) 単位がdBのすべての仕様はフルスケール±10V入力を基準にしています。 (6) フルパワー・パンドは信号/(雑音 + 歪)比が60dBに低下したときのフルスケール入力周波数で定義されます。 (7) フルスケールの 2 倍の過電圧が印加された後、仕様に規定される性能に復帰するまでの回復時間。

#### **绝**対最大定格

| かこと リロンへんこ イロ                       |                                       |

|-------------------------------------|---------------------------------------|

| アナログ入力: R1 <sub>IN</sub>            | ±25V                                  |

| R2 <sub>IN</sub>                    | ±25V                                  |

| R3 <sub>IN</sub>                    | ±25V                                  |

| CAP                                 | . +V <sub>ANA</sub> +0.3VからAGND2-0.3V |

| REF                                 | AGND2への無制限の短絡                         |

|                                     | +V <sub>ANA</sub> への瞬時短絡              |

| グランド電圧差:DGND, およびAGND2              | ±0.3V                                 |

| V <sub>ANA</sub>                    | 7V                                    |

| V <sub>DIG</sub> からV <sub>ANA</sub> | +0.3V                                 |

| V <sub>DIG</sub>                    | 7V                                    |

| デジタル入力                              | 0.3Vから+V <sub>DIG</sub> +0.3V         |

| 最大接合部温度                             | +165                                  |

| 内部消費電力                              | 700mW                                 |

| リード線の温度(10秒間の半田付け)                  | +300                                  |

|                                     |                                       |

### 静電気放電感度

静電気放電はわずかな性能の低下から完全なデバイスの故障 に至るまで、様々な損傷を与えます。すべての集積回路は、適 切なESD保護方法を用いて、取扱いと保存を行うようにして下 さい。高精度の集積回路は、損傷に対して敏感であり、極めて わずかなパラメータの変化により、デバイスに規定された仕様 に適合しなくなる場合があります。

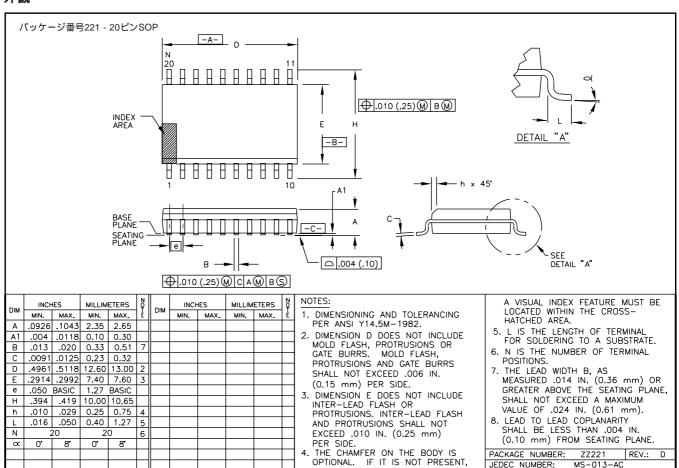

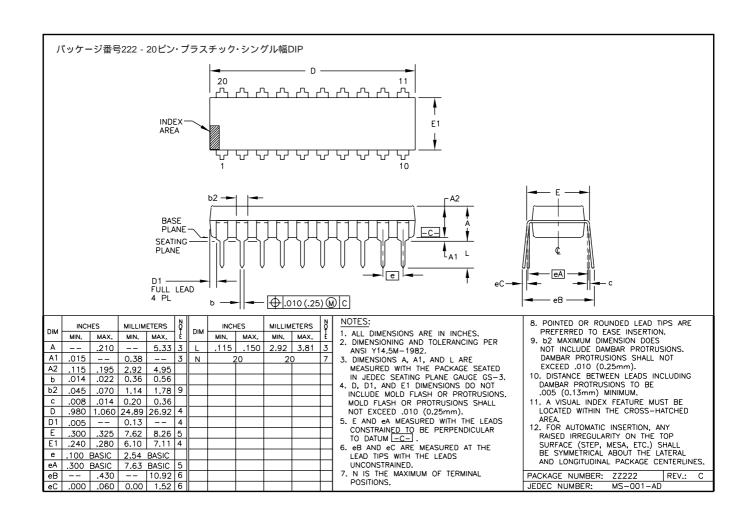

#### パッケージ情報(1)

| モデル       | パッケージ          | パッケージ図番号 |

|-----------|----------------|----------|

| ADS7808P  | 20ピン・プラスチックDIP | 222      |

| ADS7808PB | 20ピン・プラスチックDIP | 222      |

| ADS7808U  | 20ピンSOP        | 221      |

| ADS7808UB | 20ピンSOP        | 221      |

注:(1)詳細図および寸法表については、データシートの巻末を参照してください。

#### ご発注の手引き

| モデル                                            | 最大直線性誤差(LSB)                   | 最小信号/<br>(雑音+歪)<br>比(dB) | 仕様温度範囲                                           | パッケージ                                                  |

|------------------------------------------------|--------------------------------|--------------------------|--------------------------------------------------|--------------------------------------------------------|

| ADS7808P<br>ADS7808PB<br>ADS7808U<br>ADS7808UB | ±0.9<br>±0.45<br>±0.9<br>±0.45 | 70<br>72<br>70<br>72     | -40 ~ +85<br>-40 ~ +85<br>-40 ~ +85<br>-40 ~ +85 | 20ピン・プラスチックDIP<br>20ピン・プラスチックDIP<br>20ピンSOP<br>20ピンSOP |

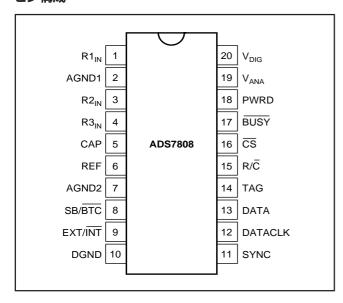

#### ピン構成

| ピン番号 | ピン名                          | 説明                                                                                                                                                             |

|------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | R1 <sub>IN</sub>             | アナログ入力。入力範囲の接続は表 と図4を参照。                                                                                                                                       |

| 2    | AGND1                        | アナログ・グランド。グランド基準点として内部で使用。電流フローを最小にして下さい。                                                                                                                      |

| 3    | R2 <sub>IN</sub>             | アナログ入力。入力範囲の接続は表 と図4を参照。                                                                                                                                       |

| 4    | R3 <sub>IN</sub>             | アナログ入力。入力範囲の接続は表 と図4を参照。                                                                                                                                       |

| 5    | CAP                          | リファレンス・バッファ・コンデンサ。2.2 μ Fタンタルをグランドとの間に接続する。                                                                                                                    |

| 6    | REF                          | リファレンス入出力。+2.5Vの内部リファレンスを出力する。外部システム・リファレンスによってもドライブ可能。いずれの場合も2.2                                                                                              |

|      |                              | μFのタンタル·コンデンサでグランドにバイパスする。                                                                                                                                     |

| 7    | AGND2                        | アナログ・グランド。                                                                                                                                                     |

| 8    | SB/BTC                       | ストレート・バイナリまたは2の補数バイナリのデータ出力フォーマットを選択する。 " ハイ " の場合、データはストレート・バイナリ・                                                                                             |

|      |                              | フォーマットで出力される。 "ロー "であれば、データは 2 の補数バイナリ・フォーマットで出力される。                                                                                                           |

| 9    | EXT/INT                      | データ転送用の外部または内部クロックを選択する。"ハイ"の場合、データはクロック入力と同期してDATACLKに出力される。"ロー"                                                                                              |

|      |                              | の場合、変換コマンドにより前の変換からのデータ転送が開始され、12個のクロック・パルスに同期してDATACLKに出力される。                                                                                                 |

| 10   | DGND                         | 「デジタル· グランド。<br>                                                                                                                                               |

| 11   | SYNC                         | 同期出力。EXT/INTが"ハイ"の場合、CS"ロー"のときにはR/Cの立ち上がりエッジで、R/Cが"ハイ"のときはCSの立ち下がりエッ                                                                                           |

|      |                              | ジで、外部DATACLKに同期してSYNCにパルスが出力される。                                                                                                                               |

| 12   | DATACLK                      | EXT/INTレベルによって入力または出力になる。出力データはこのクロックに同期化される。EXT/INTが"ロー"の場合、DATACLKは各                                                                                         |

| 1.0  | DATA                         | 変換の12クロック後に送信を行ない、変換と変換の間では"ロー"を保持する。                                                                                                                          |

| 13   | DATA                         | シリアル・データ出力。データはDATACLKに同期化され、フォーマットはSB/BTCレベルによって決定される。外部クロック・モードで                                                                                             |

|      |                              | は、12データ・ビット後に、ADS7808は、CSが " ロー " でR/Cが " ハイ " であればTAG入力のレベルを出力する(図 3 参照)。EXT/INTが │<br>" ロー " の場合、データはDATACLKの立ち上がりおよび立ち下がりの両方のエッジで有効となり、変換と変換の間では、DATAは変換が │ |

|      |                              | ロー の場合、データはDATACERの立ちエかりのよび立ち下がりの両方のエックで有効となり、変換と変換の向では、DATAは変換が「開始されたときのTAG入力のレベルを保持する。                                                                       |

| 14   | TAG                          | 開始されたこさのTAG/C/Jのアベルを味持する。<br>  外部クロック・モードで使用するタグ入力。EXT/INTが " ハイ " の場合、CSが " ロー " でR/Cが " ハイ " であれば、TAGのデジタル・デー                                                |

| '4   | IAG                          | タ入力が12 DATACLKパルス後にDATAに出力される。図3参照。                                                                                                                            |

| 15   | R/C                          | ファスカット BATAGEN (アス 後にBATA に出力 される。                                                                                                                             |

| '0   | 10,0                         | EXT/INTが " ロー " の場合にも、前の変換からのデータ結果の送信を開始する。EXT/INTが " 八イ " の場合、CS " ロー " のときR/Cの立ち                                                                             |

|      |                              | 上がりエッジ、またはR/Cが " ハイ " のときCSの立ち下がりエッジでSYNCにパルスを送信し、前の変換からのデータ送信を開始する。                                                                                           |

| 16   | cs                           | チップ・セレクト。内部でR/CとOR接続されている。                                                                                                                                     |

| 17   | BUSY                         | ビジー出力。変換が開始されると " ロー " に立ち下がり、変換が完了しデータが出力シフト・レジスタにラッチされるまで " ロー " を保                                                                                          |

|      |                              | 持する。BUSYが立ち上がったときは、CSまたはR/Cが"ハイ"でなければならない。"ハイ"でない場合は、信号アクイジションの時間                                                                                              |

|      |                              | なしで新しい変換が開始される。                                                                                                                                                |

| 18   | PWRD                         | パワー・ダウン入力。"ハイ"のとき変換が抑止され、消費電力が大幅に低減される。前の変換からの結果は出力シフト・レジスタで維                                                                                                  |

|      |                              | 持される。                                                                                                                                                          |

| 19   | V <sub>ANA</sub>             | アナログ電源入力。公称+5V。ピン20に直接接続し、0.1μFセラミックおよび10μFタンタル· コンデンサでグランドにデカップリング                                                                                            |

|      | /                            | する。                                                                                                                                                            |

| 20   | $V_{\scriptscriptstyle DIG}$ | デジタル電源入力。公称+5V。ピン19に直接接続する。V <sub>ANA</sub> と同じか、それ以下でなければならない。                                                                                                |

### ピン構成

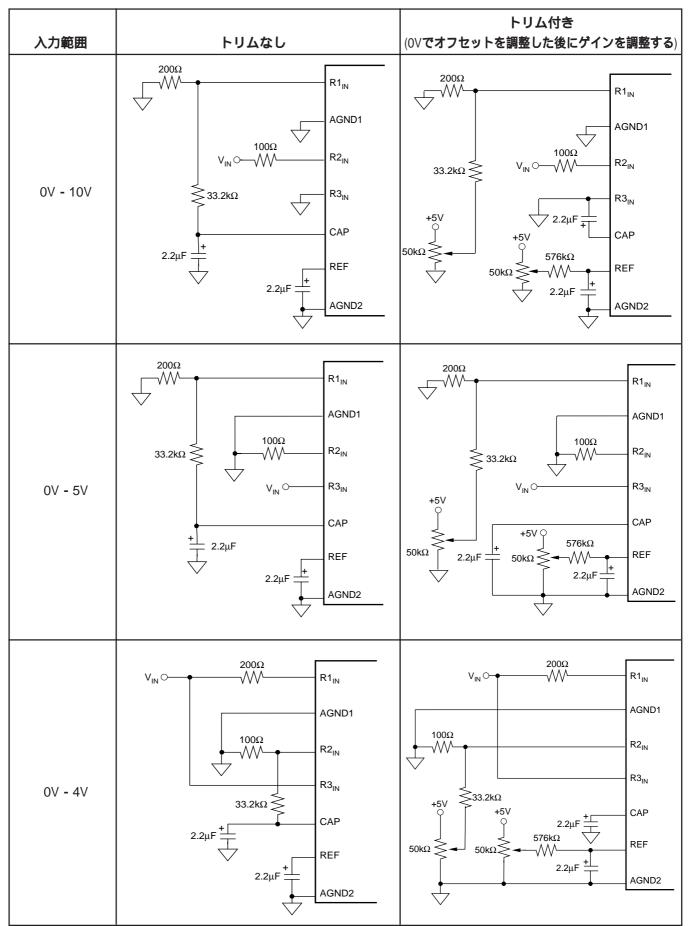

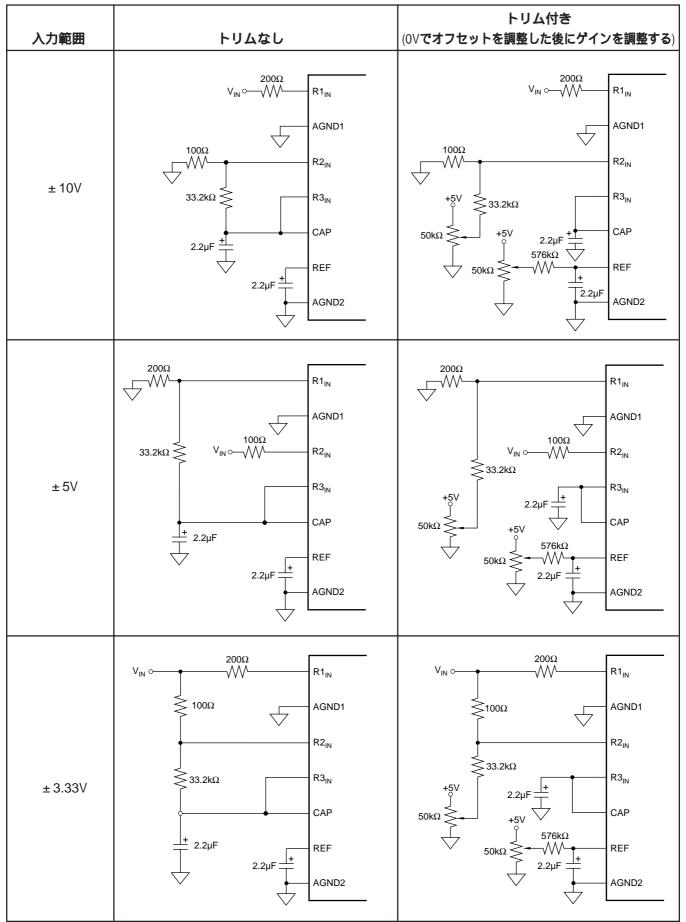

| アナログ入力範囲 | R1 <sub>IN</sub> 接続先<br>(200 を通して) | R2 <sub>IN</sub> 接続先<br>(100 <b>を通して</b> ) | R3 <sub>IN</sub> 接続先 | インピーダンス |

|----------|------------------------------------|--------------------------------------------|----------------------|---------|

| ±10V     | V <sub>IN</sub>                    | AGND                                       | CAP                  | 22.9 k  |

| ±5V      | AGND                               | V <sub>IN</sub>                            | CAP                  | 13.3 k  |

| ±3.33V   | V <sub>IN</sub>                    | V <sub>IN</sub>                            | CAP                  | 10.7 k  |

| 0V ~ 10V | AGND                               | V <sub>IN</sub>                            | AGND                 | 13.3 k  |

| 0V ~ 5V  | AGND                               | AGND                                       | V <sub>IN</sub>      | 10.0 k  |

| 0V ~ 4V  | V <sub>IN</sub>                    | AGND                                       | V <sub>IN</sub>      | 10.7 k  |

表1. 入力範囲接続。図4参照。

| 記号                             | 説明                          | 最小  | 標準  | 最大                 | 単位 |

|--------------------------------|-----------------------------|-----|-----|--------------------|----|

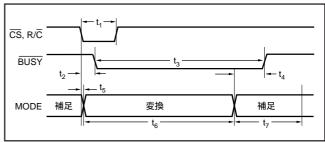

| t <sub>1</sub>                 | 変換パルス幅                      | 40  |     | 4500               | ns |

| t <sub>2</sub>                 | BUSY<br>遅延                  |     |     | 65                 | ns |

| t <sub>3</sub>                 | BUSY " □ – "                |     |     | 8                  | μs |

| t <sub>4</sub>                 | 変換終了後の<br>BUSY遅延            |     | 220 |                    | ns |

| t <sub>5</sub>                 | アパーチャ遅延                     |     | 40  |                    | ns |

| t <sub>6</sub>                 | 変換時間                        |     | 5.7 | 8                  | μs |

| t <sub>7</sub>                 | アクイジション時間                   |     |     | 2                  | μs |

| t <sub>6</sub> +t <sub>7</sub> | スループット時間                    |     | 9   | 10                 | μs |

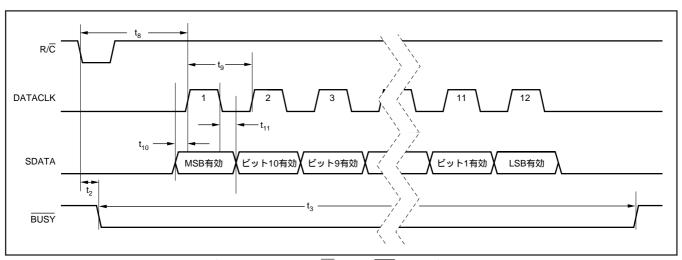

| t <sub>8</sub>                 | R/C " ロー " からDATACLK遅延      |     | 450 |                    | ns |

| t <sub>9</sub>                 | DATACLK周期                   |     | 440 |                    | ns |

| t <sub>10</sub>                | データ有効からDATACLK<br>" ハイ " 遅延 | 20  | 75  |                    | ns |

| t <sub>11</sub>                | DATACLK " ロー "<br>遅延後のデータ有効 | 100 | 125 |                    | ns |

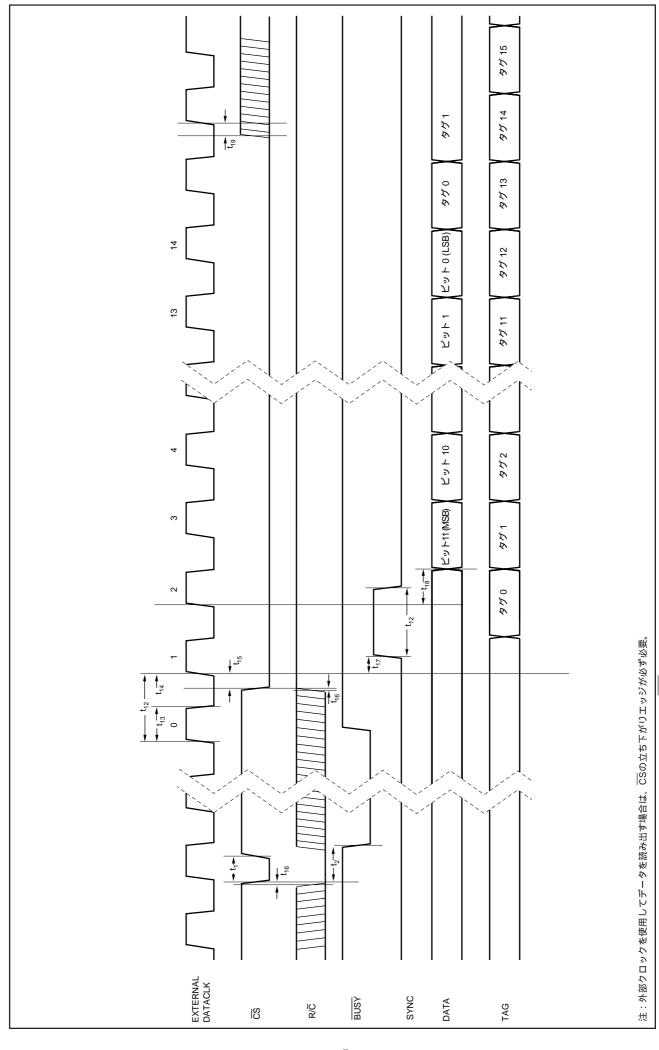

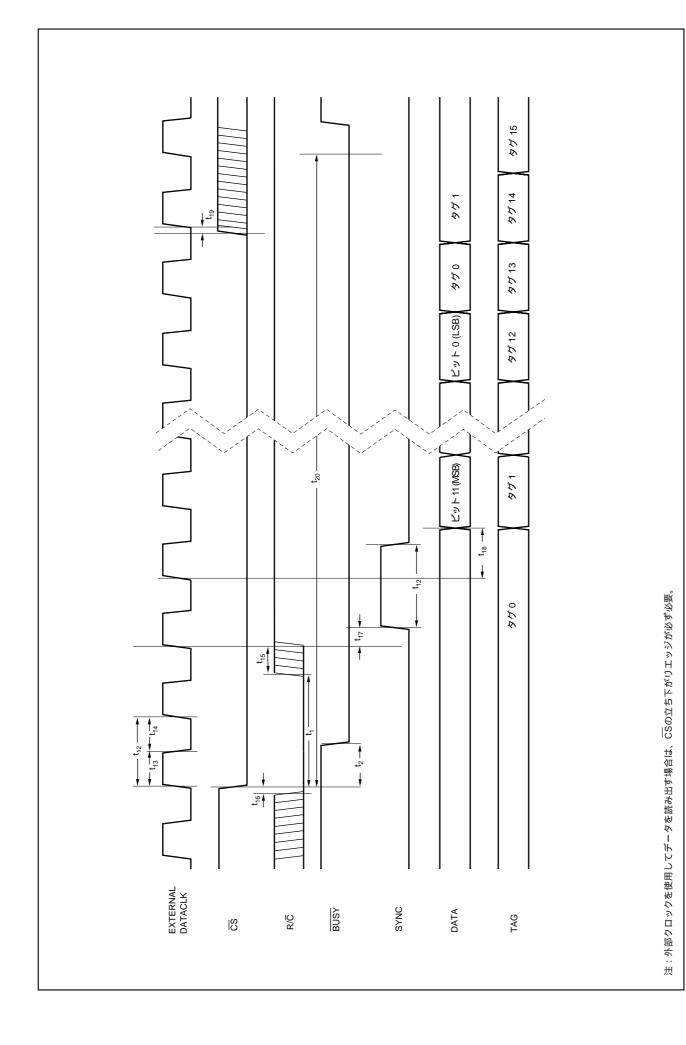

| t <sub>12</sub>                | 外部DATACLK周期                 | 100 |     |                    | ns |

| t <sub>13</sub>                | 外部DATACLK周期 " ハイ "          | 20  |     |                    | ns |

| t <sub>14</sub>                | 外部DATACLK周期 " ロー "          | 30  |     |                    | ns |

| t <sub>15</sub>                | DATACLK " ハイ "<br>セットアップ時間  | 20  |     | t <sub>12</sub> +5 | ns |

| t <sub>16</sub>                | R/CからCSまでの<br>セットアップ時間      | 10  |     |                    | ns |

| t <sub>17</sub>                | DATACLK " ハイ " 後の<br>SYNC遅延 | 15  |     | 35                 | ns |

| t <sub>18</sub>                | データ有効遅延                     | 25  |     | 55                 | ns |

| t <sub>19</sub>                | <br>CSからの立ち上がりエッジ遅延         | 25  |     |                    | ns |

| t <sub>20</sub>                | <br>CS " ロー " 後のデータ有効       | 4.5 |     |                    | μs |

図1. 基本的な変換タイミング

表II. 変換およびデータ・タイミング。T<sub>A</sub>=-40 から+85 。

図2. 内部クロックを使用したシリアル・データ・タイミング。(CS、EXT/INT、およびTAGを'ロー "に接続)

| 機能                        | CS    | R/C   | BUSY  | EXT/INT | DATACLK | PWRD | SB/BTC | 動作                                                                                                  |

|---------------------------|-------|-------|-------|---------|---------|------|--------|-----------------------------------------------------------------------------------------------------|

| 変換開始と内部クロック<br>を使用したデータ出力 | 1 > 0 | 0     | 1     | 0       | 出力      | 0    | х      | 変換"n"を開始する。変換"n-1"からのデータが<br>DATACLKに出力される12個のクロック・パルスに同<br>期してDATAにクロック・アウトされる。                    |

|                           | 0     | 1 > 0 | 1     | 0       | 出力      | 0    | х      | 変換"n"を開始する。変換"n-1"からのデータが<br>DATACLKに出力される12個のクロック・パルスに同<br>期してDATAにクロック・アウトされる。                    |

| 変換開始と内部クロック               | 1 > 0 | 0     | 1     | 1       | 入力      | 0    | х      | 変換" n " を開始する。                                                                                      |

| を使用したデータ出力                | 0     | 1 > 0 | 1     | 1       | 入力      | 0    | x      | 変換" n " を開始する。                                                                                      |

|                           | 1 > 0 | 1     | 1     | 1       | 入力      | Х    | х      | SYNCにパルスを出力する。続いて変換"n"からの<br>データが外部DATACLKに同期してクロック・アウト<br>される。                                     |

|                           | 1>0   | 1     | 0     | 1       | 入力      | 0    | х      | SYNCにパルスを出力する。続いて変換 " n-1 " から<br>のデータが外部DATACLKに同期してクロック・アウ<br>トされる。 <sup>(1)</sup> 変換 " n " は実行中。 |

|                           | 0     | 0 > 1 | 0     | 1       | 入力      | 0    | х      | SYNCにパルスを出力する。続いて変換 " n-1 " から<br>のデータが外部DATACLKに同期してクロック・アウ<br>トされる。 <sup>(1)</sup> 変換 " n " は実行中。 |

| 誤变換                       | 0     | 0     | 0 > 1 | х       | х       | 0    | х      | <br>CSまたはR/Cが " ハイ " でないと、アクイジション<br>時間をとらずに新しい変換が開始される。                                            |

| パワー・ダウン                   | х     | х     | x     | x       | x       | 0    | х      | アナログ回路に給電する。変換は進行可能。                                                                                |

|                           | х     | х     | х     | х       | х       | 1    | х      | アナログ回路をディスエーブルする。前の変換から<br>のデータは出力レジスタに維持されている。                                                     |

| 出力フォーマットの選択               | х     | х     | х     | х       | х       | Х    | 0      | シリアル·データが2の補数バイナリ·フォーマット<br>で出力される。                                                                 |

|                           | х     | Х     | х     | х       | х       | Х    | 1      | シリアル· データがストレート· バイナリ· フォーマッ<br>トで出力される。                                                            |

注:(1)変換中に前データ有効に関する制約については図3bを参照して下さい。

#### 表III. コントロール真理値表

|                  |          |          |            |          |                                        |                    |                          | デジタ                | ル出力            |     |

|------------------|----------|----------|------------|----------|----------------------------------------|--------------------|--------------------------|--------------------|----------------|-----|

|                  |          |          |            |          | <b>2 の補数バイ</b><br>(SB/BTC " <b>ロ</b> - |                    | ストレート・バイ<br>(SB/BTC " ハイ | · · I              |                |     |

| 説明               |          |          | アナログ       | 入力       | バイナリ・コード                               | 16 <b>進</b><br>コード | バイナリ・コード                 | 16 <b>進</b><br>コード |                |     |

| フルスケール・レンジ       | ±10      | ±5       | ±3.33V     | 0V to 5V | 0V to 10V                              | 0V to 4V           |                          |                    |                |     |

| 最下位ビット(LSB)      | 4.88mV   | 2.44mV   | 1.63mV     | 1.22mV   | 2.44mV                                 | 0.98mV             |                          |                    |                |     |

| +フルスケール(FS-1LSB) | 9.99512V | 4.99756V | 3.33171V   | 4.99878V | 9.99756V                               | 3.99902V           | 0111 1111 1111           | 7FF                | 1111 1111 1111 | FFF |

| ミッドスケール          | 0V       | 0V       | 0V         | 2.5V     | 5V                                     | 2V                 | 0000 0000 0000           | 000                | 1000 0000 0000 | 800 |

| ミッドスケールから1LSB以下  | -4.88mV  | -2.44mV  | -1.63mV    | 2.49878V | 4.99756V                               | 1.99902V           | 1111 1111 1111           | FFF                | 0111 1111 1111 | 7FF |

| -フルスケール          | -10V     | -5V      | -3.333333V | 0V       | 0V                                     | 0V                 | 1000 0000 0000           | 800                | 0000 0000 0000 | 000 |

表心 理想入力電圧と出力コード

図3a.外部クロックを使用した変換とリードのタイミング。(EXT/INTを"ハイ"に接続)変換後に読み出し

図3b. 外部クロックを使用した変換とリードのタイミング。(EXT/INTを"ハイ"に接続)変換中に読み出し(前の変換結果)

図4a. ユニポーラ入力範囲用オフセット/ゲイン回路

図4b. バイポーラ入力範囲用オフセット/ゲイン回路

#### 外観