# Application Note

## PCM1723**のクロック・** インターフェースとジッタ性能

このアプリケーションノートは、PCM1723内蔵のPLL部の 構成および生成システムクロックのジッタ性能、クロック・ インターフェースの実際について実測データも含めて解説し たものです。

特に、各種DVD応用製品やセット・トップ・ボックス等 MPEG2アプリケーションでの応用法について、実設計の参 考資料として役立てていただければ幸いです。

#### 27MHzマスター·クロックの入出力

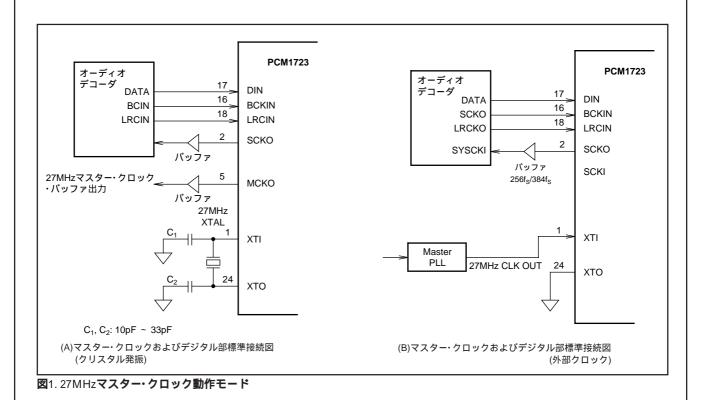

PCM1723では、図1に示す通り、基本的に27MHzマスター・クロックをクリスタルで自己発振する動作モードと外部入力する動作モードがあります。この27MHzクロックは当然、MPEGデコーダICにも使用されますが、この時のインターフェース方法に関しては一考を要します。

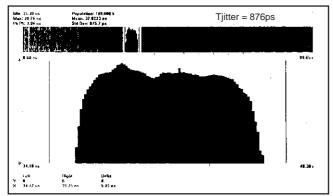

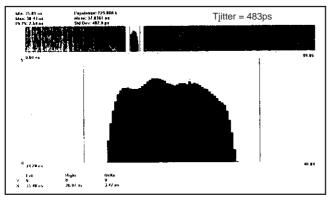

PCM1723は、27MHzマスター・クロックのバッファ出力がMCKO端子より出力されますが、このMCKO出力は内部構成上、ジッタを若干含んでいます。図2にMCKO出力でのジッタの実測データを示します。図2Aはクリスタル発振の場合で、図2Bは外部入力の場合をそれぞれ示しています。

このデータから明らかなように、いずれの場合も480psecから900psecのジッタがあります。このMCKOクロックはMPEGデコーダICにインターフェースされますが、MPEGデコーダICによっては27MHzマスター・クロック入力のジッタについて規定しているものがあり、その許容ジッタ・レベルを満足しないかもしれません。また、MCKO端子自体はスイッチング動作における電流ノイズでのオーディオ特性への影響を避けるため、ドライブ能力を抑えてあります。したがって、27MHzマスター・クロックのインターフェースを考えた場合、MCKO端子の使用はなるべく避けた方が良いと判断できます。

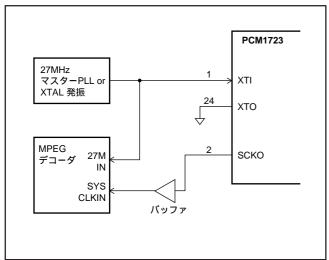

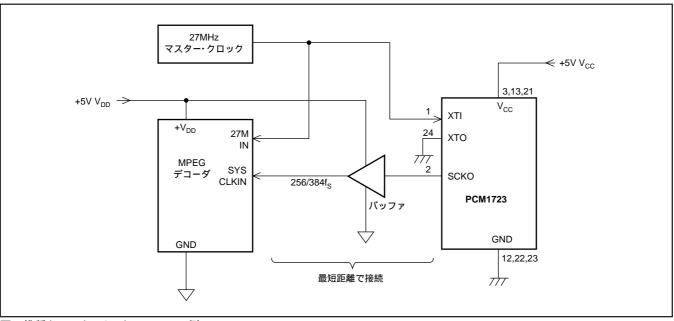

図3にこれらを考慮したインターフェース例を示します。この例では、27MHzマスター・クロックがクリスタル発振クロックの場合でも、前段のPLLクロックの場合でもPCM1723のXTI端子に入力すると同時に、MPEGデコーダICにもパラレルに供給する方式としています。これにより、MCKO端子のジッタの影響は全くなくなり、余計なトラブルを避けることができます。

図2A. MCKOジッタ(クリスタル発振)

**図**2B. MCKOジッタ(外部クロック入力)

**図**3. 27MHz**クロック接続例**

#### 内蔵PLLの構成と性能

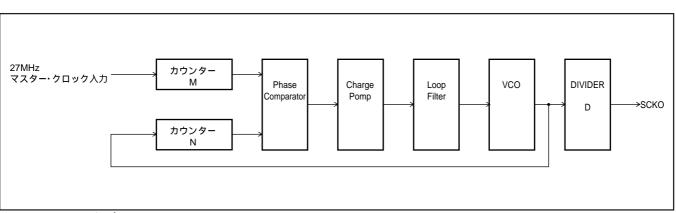

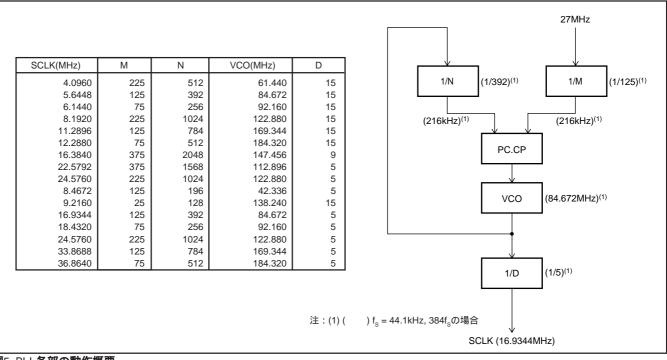

PCM1723で用いたPLL部のブロック図を図4に、また、 $256f_s$ および $384f_s$ を生成するための内部動作の概要を図5にそれぞれ示します。

PLL部は、主にM、NビットのカウンターとPhase Comparator、Charge Pomp、Loop Filter、高速VCO、デバイダDで構成されています。クリスタル発振並みの周波数精度と低ジッタ特性を確保するため、VCOの発振周波数は極めて高い周波数での安定動作を条件に設計されており、実際の最高動作周波数は実に、184.32MHzに設定されています。また、例えば、 $f_s$  = 44.1kHzに対する384 $f_s$ のシステムクロック、f = 16.9344MHzを正確に生成するため、カウンタM、Nの桁数とデバイダDの桁数は数学的にその最適構成を求めて設定されており、27MHzの周波数から、下限は4.096MHz(256 $f_s$ 、 $f_s$  = 16kHz)、上限は36.864MHz(384 $f_s$ 、 $f_s$  = 96kHz)といった極めて広範囲な周波数を理論誤差無しで生成することができます。

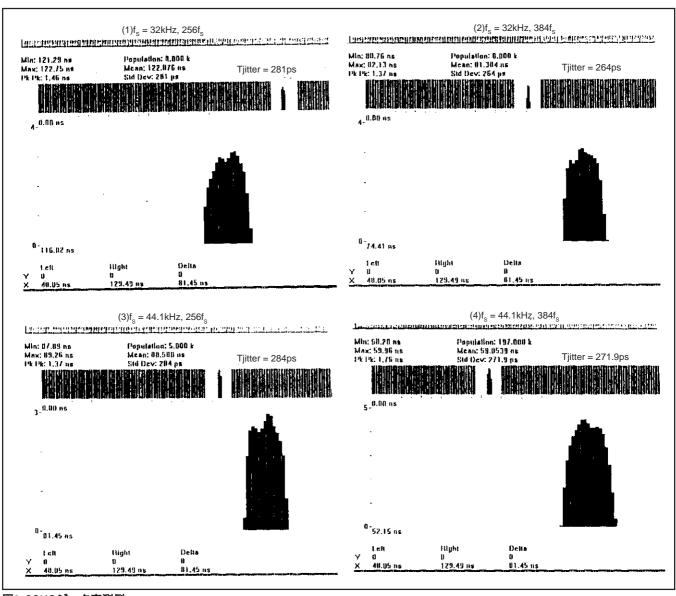

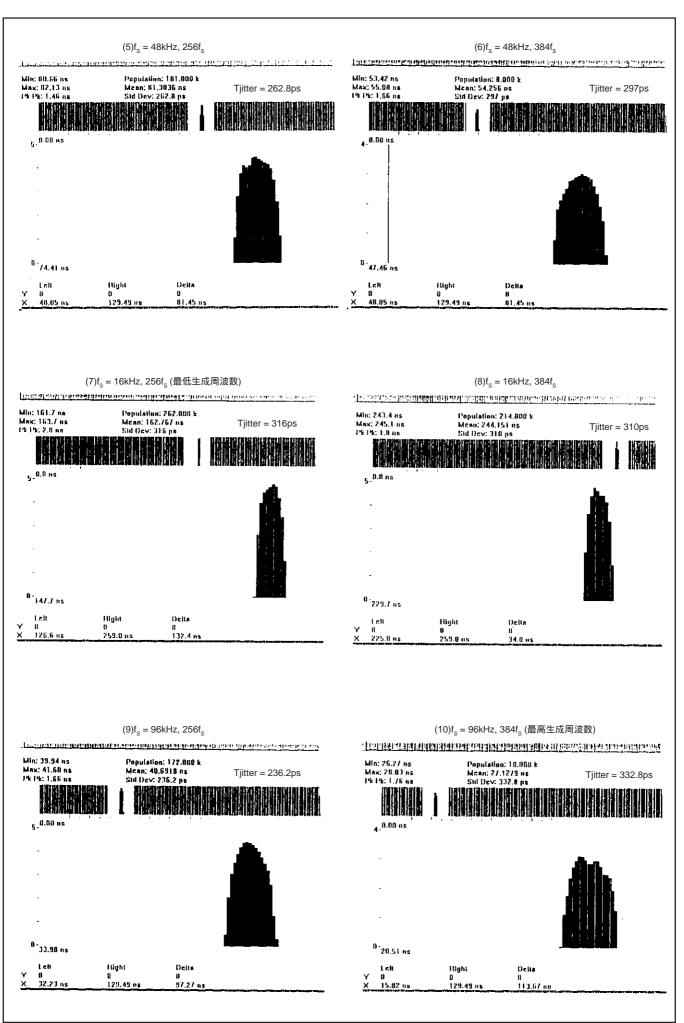

このように、PCM1723の内蔵PLLは極めて優秀な性能を有しています。実際の生成システムクロックはSCKO端子から出力されますが、システムクロック・ジッタはD/A変換性能に影響するため低ジッタであることが要求されます。図6にSCKO端子でのジッタの実測例を示します。実測データから分かる通り、PCM1723の生成システムクロック・ジッタはほぼ、200psecから330psecであり、これは他の市販のどのMPEG再生用PLLよりも優れていると言えます。

(全てのジッタ実測データは標準値です。測定はHp社タイム・インターバル・アナライザによるもので、データ中のStd Dev がジッタの実効値(rms)を意味しています。)

**図**4. PCM1723 PLL**部ブロック図**

図5. PLL各部の動作概要

**図**6. SCKO**ジッタ実測例**

#### SCKO端子のドライブ能力とオーディオ特性

PLL部で生成した256f<sub>s</sub>または384f<sub>s</sub>のシステムクロックは、そのままPCM1723自体のDAC動作用クロックとして用いられ、これは内部で接続されています。一方、このシステムクロックは一般的にMPEGデコーダICのオーディオ用基準動作クロックとして、PCM1723のSCKO端子からMPEGデコーダICへ供給されます。

ここで、先のMCKO端子のところでも触れましたが、SCKO端子も一般的なCMOS ICと比べて十分なドライブ能力を持っていないため、外部へのインターフェースには外部パッファを介して接続することを推奨します。この外部パッファは、PCM1723自体のオーディオ特性の劣化を避ける目的と、システムクロックの供給先であるMPEGデコーダICの入力タイミング規定への合致を目的としています。

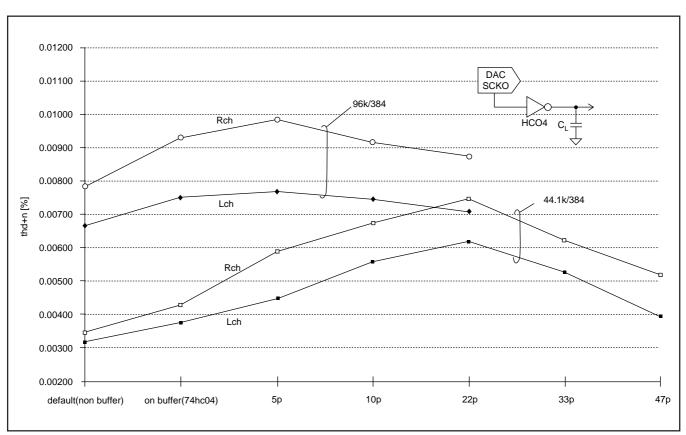

具体的には、図7にPCM1723の負荷容量対THD+N特性の実測例を示します。この図7のデータから分かる通り、SCKO端子の負荷容量が大きくなると、SCKO端子での負荷電流が増え、これは非常に高速であるため、DAC部の電源にも影響し、結果的にTHD+N特性に悪影響します。

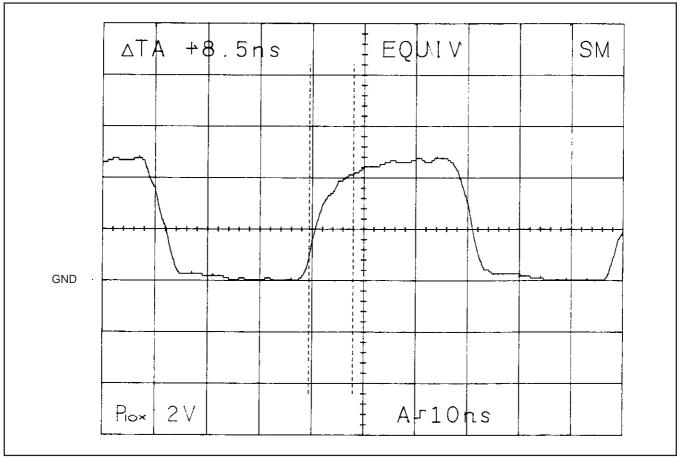

もうひとつの具体的例は、SCKO端子でのクロック出力の立ち上がリ/立ち下がり時間の特性とMPEGデコーダICにおける入力

クロックへの要求性能の関係です。図8にSCKO端子でのクロック実測波形を示します。10% of  $V_{DD}$ から90% of  $V_{DD}$ への遷移時間は8nsecから9nsecです ( $f_s$  = 44.1kHz、 $394f_s$  = 16.9344MHz)。この遷移時間は特に遅いものではありませんが、MPEGデコーダICによっては、この遷移時間の規定を4nsecとしているものがあり、この要求仕様を満足させるには、外部バッファの接続が絶対に必要となります。

すなわち、MPEGデコーダICとのインターフェース・タイミングおよびPCM1723自体のオーディオ特性を満足させる意味でSCKO端子の出力には外部パッファを必ず接続して下さい。また、ここで用いるパッファICの電源系はPCM1723のアナログ系を用いるのではなく、MPEGデコーダIC側のデジタル系電源に接続して下さい。これらを考慮した接続例を図9に示します。ここでは詳しく触れませんでしたが、27MHzマスター・クロック、256f<sub>s</sub>/384f<sub>s</sub>システムクロック供にその周波数はMHzオーダーの高周波数クロックであり、その接続はできる限り最短距離で行って下さい。

図7. SCKO負荷容量対THD+N特性

図8. SCKO出力波形(C, = 15PF) クロック周波数 = 16.9344MHz

図9. 推奨クロック・インターフェース例

このアプリケーションノートに記載されている情報は、信頼しうるものと考えておりますが、不正確な情報や記載漏れ等に関して弊社は責任を負うものではありません。情報の使用について弊社は責任を負えませんので、各ユーザーの責任において御使用下さい。価格や仕様は予告なしに変更される場合がありますのでご了承下さい。ここに記載されているいかなる回路についても工業所有権その他の権利またはその実施権を付与したり承諾したりするものではありません。弊社は弊社製品を生命維持に関する機器またはシステムに使用することを承認しまたは保証するものではありません。

### 日本バー・ブラウン株式会社

http://www.bbj.co.jp/

本 社 〒222-0033 横浜市港北区新横浜2-3-12 新横浜スクエアビル ● 045-476-7870

大阪営業所 〒532-0011 大阪市淀川区西中島6-1-1 新大阪プライムタワー ● 06-6305-3287

万一つながらない場合は、お手数ですが弊社営業部FAX045-476-7889 (有料)までご送信くださるか、あるいはTELにてお問い合わせください。

(AB-JPN)