# Application Note

## PCM1732 **における** HDCD**対応ゲイン・スケーリング**

このアプリケーションノートはHDCD\*デコーダ内蔵 DAC、PCM1732におけるHDCD再生に対応した、ゲイン・ スケーリングの原理とアプリケーション例について解説し ています。

\* HDCDはPacific Microsonics Inc.の登録商標です。

#### HDCDの基準レベル

HDCD方式では、エンコード(録音)時においては、ピーク・エクステンド有り、またはピーク・エクステンド無しの2種類の方式が用いられており、その選択は主に録音サイドの判断によります。このピーク・エクステンド有り、無しの情報は、HDCD方式のHidden Codeとともにエンコード(録音)時に記録され、HDCDデコード時はこれらの情報を抽出します。PCM1732においては、このピーク・エクステンド有り、無しはゲイン・ピン(ピン20)から、HDCD方式の情報はHDCDピン(ピン9)からそれぞれ出力されます。

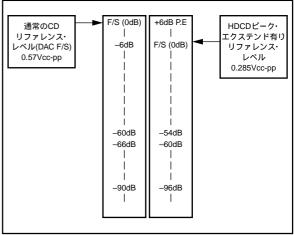

ディスクに記録される信号レベルの基準レベルは、このピーク・エクステンド有り、無しで6dB差があり、このレベル差は何らかの手法で補正しなければなりません。図1にこれらの関係を示します。通常CDとHDCDのピーク・エクステンド無しの信号基準レベルは同じですが、HDCDのピーク・エクステンド無しの場合に比べて、6dB基準レベルが低くなっています。したがって、HDCD対応CDプレーヤにおいては、この両者のレベル差を補正しなければなりません。

#### ゲイン・スケーリング

前述の通常CDおよびHDCDピーク・エクステンド無しと HDCDピーク・エクステンド有りのレベル差の補正を、ゲイン・スケーリングとここでは定義します。このゲイン・スケーリングの手法には大別すると次の2種類の手法があります。

- 1. デジタル・スケーリング

- 2. アナログ・スケーリング

それぞれの手法の原理を簡単に説明すると、デジタル・スケーリングはPCM1732に内蔵してあるデジタルフィルタのアッテネータ機能を用いる手法で、アナログ・スケーリングは外部にアナログ・ゲイン切り替え回路を用いる手法です。

図1.ピーク・エクステンド有り、無し時のレベルの差の関係

#### デジタル・スケーリング

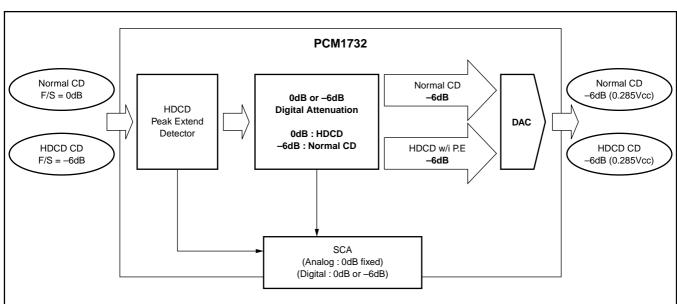

デジタル・スケーリングの機能はPCM1732に内蔵されており、イニシャルの状態ではこのデジタル・ゲイン・スケーリングが自動的に機能するようになっています。デジタル・ゲイン・スケーリングでのディスク別の信号フローを図2に示します。デジタル・ゲイン・スケーリングでは、HDCDピーク・エクステンド有りの信号はそのままスルーしますが、HDCDピーク・エクステンド無しおよび通常CDの信号は6dBアッテネーションされます。この-6dBゲインにより、信号レベルはピーク・エクステンド有りの信号レベルと同じレベルになります。このデジタル・ゲイン・スケーリングの特長は、

- 外部に何らの補正回路を必要としない

- 通常CD、HDCDピーク・エクステンド無しの信号はデジ タル領域で6dB減衰させるので、6dBのレベル低下と、 ほぼ1ビット分の量子化ロス(THD+N等のオーディオ特 性の劣化)を発生する。

したがって、このデジタル・ゲイン・スケーリングを選択した場合、通常CDおよびHDCDピーク・エクステンド無しのディスク(信号)に対するオーディオ特性の劣化を認識しておかなければなりません。なお、このデジタル・ゲイン・スケーリングとアナログ・ゲイン・スケーリングに切り替えは、PCM1732のソフトウェア制御(モードレジスタ2、SCA)で行うことができます。

#### アナログ・ゲイン・スケーリング

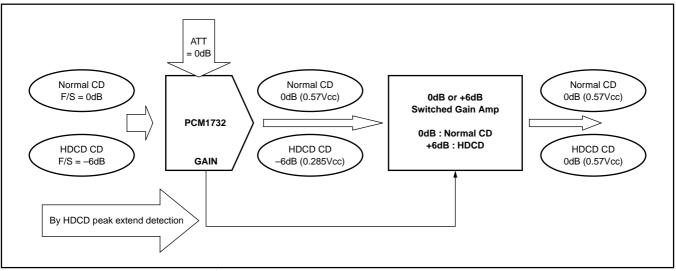

アナログ・ゲイン・スケーリングでのディスク別信号フローを図3に示します。アナログ・ゲイン・スケーリングでは、ゲイン・ピンからの通常CDおよびHDCDピーク・エクステンド無しとHDCDピーク・エクステンド有りの検出出力(HまたはL)によって、0dBまたは6dBのゲイン切り替えを外部アナログ・ゲイン回路で行います。通常CDおよびHDCDピーク・エクステンド無しの信号に対しては0dBゲイン、HDCDピーク・エクステンド有りの信号に対しては+6dBゲインをかけ、両信号のレベルを合わせます。このアナログ・ゲイン・スケーリングの特長は

- ◆ 外部にデジタル制御アナログ・ゲイン回路(0dB/+6dB)を必要とする

- デジタルによるオーディオ特性の劣化がない。ただし、外部アナログ・ゲイン回路はDAC性能に応じたオーディオ特性(両ゲインにて)を要求される。

したがって、アナログ・ゲイン・スケーリングでは、この外部ア ナログ・ゲイン回路の設計がキーポイントとなります。PCM1732 のTHD + N特性は標準で0.0015%ですから、この低歪み特性を満足するアナログ・ゲイン回路を設計しなければなりません。

#### アナログ・ゲイン回路

ここでは、アナログ・ゲイン・スケーリングにおけるデジタル制御アナログ・ゲイン回路の設計例を示します。アナログ・ゲイン回路の構成を考えた場合、そのゲイン制御の手法で大別すると

- リレーによるゲイン切り替え

- トランジスタによるゲイン切り替え

があります。また、コスト面からはポスト・ローパスフィルタの機能を兼用させる場合も考えられます。ここでは、これらを考慮 し2種類のアナログ・ゲイン回路の例を示します。

#### リレーによるアナログ・ゲイン回路

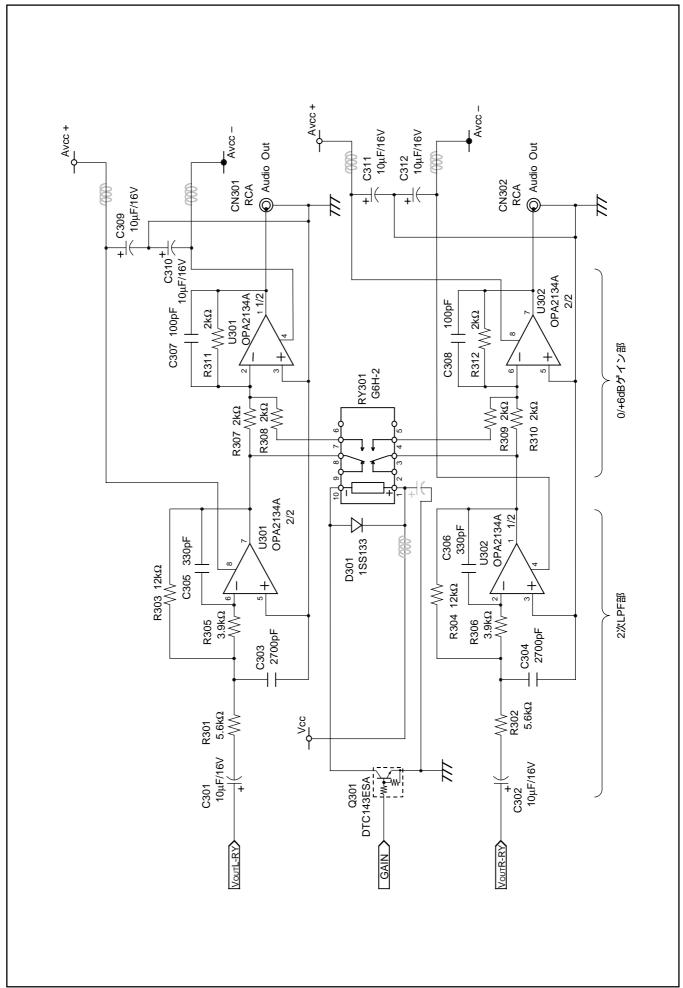

リレーによるアナログ・ゲイン回路の例を図4に示します。この 回路はチャンネルあたり2個のオペアンプで構成され、1段目はポ スト・ローパスフィルタ、2段目は0dB/+6dBのゲイン回路として

図2. デジタル・ゲイン・スケーリングでのディスク別信号フロー

図3. アナログ・ゲイン・スケーリングでのディスク別信号フロー

図4. リレーによるアナログ・ゲイン回路例

動作します。ポスト・ローパスフィルタ段は、ゲイン、fc(カットオフ周波数)を決定する定数は固定であり、2段目の反転増幅回路の抵抗比をリレーで切り替えます。したがって、ゲイン切り替えを行ってもローパスフィルタとしての特性は変化しません。また、切り替えをリレーで行うため、半導体での場合に見られる非線型特性の影響が一切ありません。

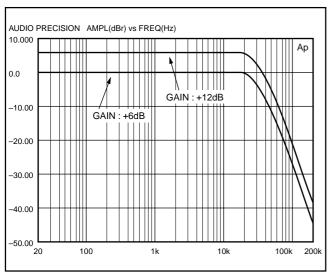

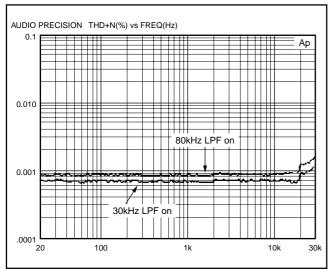

このリレーによるアナログ・ゲイン回路での総合周波数特性とTHD+N特性の実測例を図5、図6にそれぞれ示します。この回路での注意点のひとつは最大信号振幅です。HDCDピーク・エクステンド有りのディスクでは、その言葉からも明らかなように、基準レベルを超えるピーク信号が含まれている場合があります。すなわち、通常のオーディオ出力レベルは2Vrms、約6Vp-pですが、このレベルより最大6dB大きいピーク信号があった場合、オーディオ出力レベルは通常の倍の4Vrms、12Vp-pとなります。したがって、12Vp-pの最大信号振幅を設計仕様に考慮しなければなりません。

図5. リレー仕様フィルタ回路単体周波数特性

図6. リレー仕様フィルタ回路単体THD + N特性

#### トランジスタによるアナログ・ゲイン回路

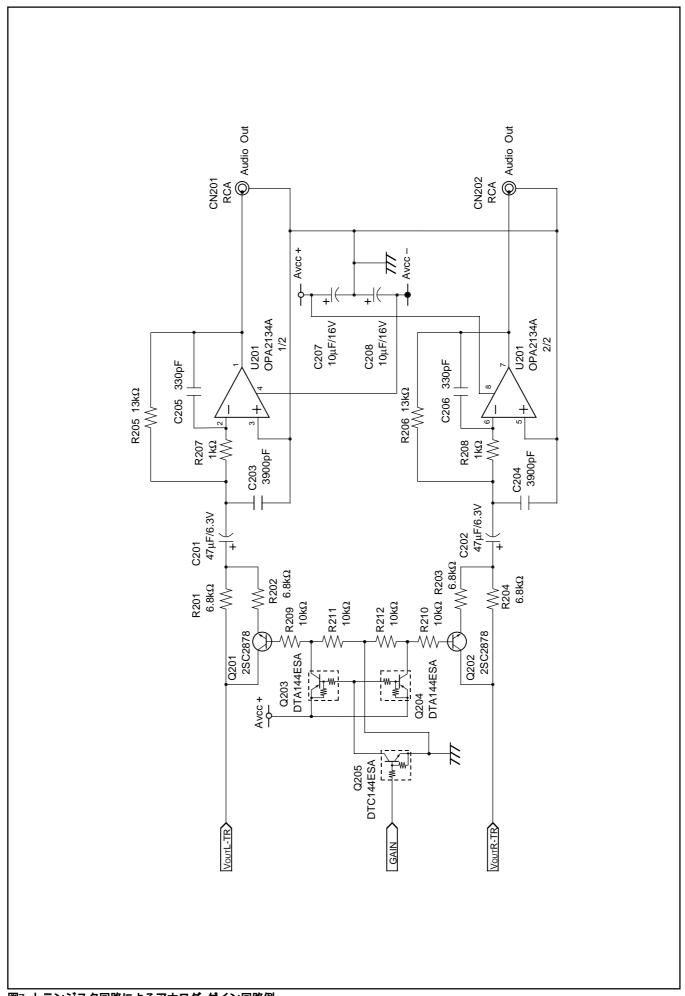

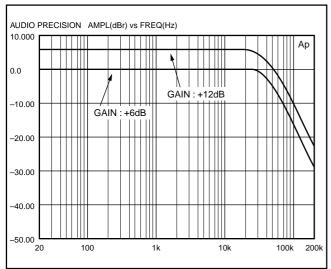

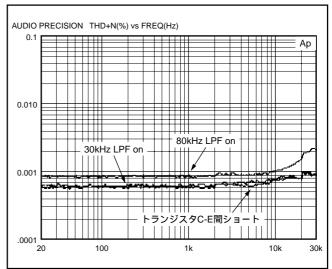

トランジスタによるアナログ・ゲイン回路の例を図7に示します。この回路では、ポスト・ローパスフィルタ機能とゲイン切り替え機能を1つのオペアンプで実現しています。通常、アクティブ・ローパスフィルタの設計ではゲインによりQの値が変化するので周波数特性も変化してしまいますが、この回路ではローパスフィルタ特性をできる限り変化させず、トランジスタによる抵抗のスイッチングで、6dB/12dBのゲイン切り替えを行っています。このトランジスタによるアナログ・ゲイン回路での総合周波数特性とTHD+N特性の実測例を図8、図9にそれぞれ示します。この回路での注意点には、同様に最大信号振幅がありますが、基本的に最も重要なのはスイッチング用トランジスタの選択です。ここで使用するトランジスタはVcc(sat)の小さい、ON抵抗の低いものを選択して下さい。

トランジスタ・スイッチによるスケーリングを行う場合のアプリケーション上の注意点について、デモボードに採用されている回路(図7)を例にとり、以下に解説します。まず、半導体スイッチによる非線形特性への影響を出来る限り抑えるために、2SC2878(Q201・202)に対してはON/OFF時とも、充分な電位でパイアスをかける必要があります。本回路ではON時のプラス側パイアスをアナログ電源A<sub>VCC</sub> + OF、OFF時のマイナス側をGNDに設定しています。ただし、DAC出力後のACカップリング・コンデンサC201・202がトランジスタ・スイッチより前段にある場合には、オーディオ信号の振幅がマイナス側まで振れるため、パイアスをA<sub>VCC</sub>-にしなければなりません。

パイアス電流量による特性への影響としては、ペース抵抗 (R209・210・211・212) の値が大きければ非線形特性の劣化、抵抗 値が小さければVcc(sat)の増加による弊害やチャンネル・セパ レーションの劣化がトレードオフの関係で存在します。非線形特 性の劣化については、バイアス量の増加によってのみ改善される と考えられます。 Voc sat )の増加は、スイッチ時のレベルシフト によるノイズと、後段のゲインアンプでの直流分増幅による飽和 などが懸念されます。直流分増幅の問題では、サンプル回路の様 に、スイッチの後にACカップリング・コンデンサを入れることに より回避出来ます。スイッチング・ノイズは、バイアスを減らし てシフト量を抑え、スイッチング・スピードを遅くすることによ り低減可能と考えられます。 チャンネル・セパレーションについ ては、理論的には電源・GNDのインピーダンスがゼロと考えて、 問題にならない筈なのですが、実際には周辺回路や基板の設計状 態により、ベース抵抗を介したL-R間の信号干渉が見受けられま す。対策としては電源・GNDインピーダンス改善が正論ですが、 これが及ばない場合には、ベース抵抗値を大きくすることによ り、干渉の抑制が可能です。サンプル回路のように、Q203 L 側、Q204 R側として別々の電流供給路を設けることも有効な手 段です。

図7. トランジスタ回路によるアナログ・ゲイン回路例

図8. トランジスタ仕様フィルタ回路単体周波数特性

図9. トランジスタ仕様フィルタ回路単体THD + N特性

このアプリケーションノートに記載されている情報は、信頼しつるものと考えておりますが、不正確な情報や記載漏れ等に関して弊社は責任を負うものではありません。情報の使用について弊社は責任を負えませんので、各ユーザーの責任において御使用下さい。価格や仕様は予告なしに変更される場合がありますのでご了承下さい。ここに記載されているいかなる回路についても工業所有権その他の権利またはその実施権を付与したり承諾したりするものではありません。弊社は弊社製品を生命維持に関する機器またはシステムに使用することを承認しまたは保証するものではありません。

### 日本バー・ブラウン株式会社

http://www.bbj.co.jp/

大阪営業所 〒532-0011 大阪市淀川区西中島6-1-1 新大阪プライムタワー ● 06-6305-3287

万一つながらない場合は、お手数ですが弊社営業部FAX045-476-7889(有料) までご送信くださるか、あるいはTELにてお問い合わせください。

(AB-JPN)